# A Single-Chip 60-V Bulk Charger for Series Li-Ion Batteries With Smooth Charge-Mode Transition

Shang-Hsien Yang, Student Member, IEEE, Jen-Wei Liu, and Chua-Chin Wang, Senior Member, IEEE

Abstract—In this paper, a single-chip 60-V battery charger prototype is presented. The newly proposed charge mode transition can ensure smooth transitions between incremental current (IC), constant current (CC), and constant voltage (CV) modes. The charger sources a current of 136 mA in CC mode and has an efficiency up to 92% during the charging sequence. Intentional saturation of both the IC and CV regulation loops ensure the stability of the charger throughout the charging sequence. Bonding PAD designed to remove the constraints on the aspect ratio of input transistors as a prevention of antenna effect is also disclosed. The proposed design has been implemented on silicon using the TSMC 0.25  $\mu$ m 1-poly 3-metal bipolar-CMOS-DMOS (BCD) 60-V process.

Index Terms—Antenna effect, charger, constant current, constant voltage, high voltage integrated circuit, incremental current.

## I. INTRODUCTION

▼ LOBAL warming due to greenhouse gas emission such as  $CO_2$  and  $CH_4$  has attracted very much attention of governments and organizations worldwide. To respond to the exigent call for greener means of transportation and miscellaneous collection of applications, the development of vehicles and other mobile systems electrically powered by batteries are beginning to gain momentum. Until now, a great majority of power management systems that require at least tens of volts must be implemented using discrete power electronic devices. The incapability of MOS transistors in a modern integrated circuit process to sustain high voltages render the implementation of high voltage (HV) power management circuits using an integrated system-on-chip (SoC) solution impossible. For such reasons, integrated power management solutions are limited to particular applications such as smart phones, tablet PCs, digital cameras, etc., where only a low supply voltage is required.

To overcome this limitation, certain HV processes with vertical double-diffused MOS (VDMOS) devices have been

The authors are with the Department of Electrical Engineering, National Sun Yat-Sen University, Kaohsiung, Taiwan 80424 (contact author: C. C. Wang) (e-mail: ccwang@ee.nsysu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2011.2177137

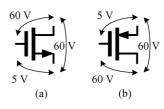

Fig. 1. The maximum sustainable voltages between different terminals of: (a) N-type, and (b) P-type LDMOS transistors.

developed to meet the demand of HV applications [1]. However, the channel length of the transistors implemented using these processes does not depend on the resolution of the photolithography. Instead, it is controlled by the lateral spreads of phosphorus and boron diffusions. The non-planar characteristics make integration of these devices into standard digital CMOS processes very difficult [2]. An alternative approach around this problem is to use lateral double-diffused MOS (LDMOS) transistors. These devices have lateral drift extension, which is similar to transistors in a standard digital CMOS process. The integration of such devices and the standard digital CMOS process has been reported in [3]. After almost a decade of advancement in semiconductor technologies, mass production using such a process, like the TSMC 0.25  $\mu m$  bipolar-CMOS-DMOS (BCD) HV process [4] used to carry out the design, is now feasible. This process offers a variety of devices to meet different requirements of various applications [5]. The design of low voltage analog circuits as well as cell-based standard digital library designs can be carried out using 0.25  $\mu m$  standard CMOS. High performance analog circuits operating at a supply voltage of 5 V can be designed using 0.5  $\mu m$  standard CMOS. Asymmetrical N-type and P-type LDMOS transistors that can support up to 60 V are adequate for HV applications. It is important to highlight that the maximum sustainable voltages between the three terminals are not equivalent. As depicted in Fig. 1, the gate-drain and drain-source voltages can endure up to 60 V, but the maximum voltage between gate and source is strictly limited to 5 V only.

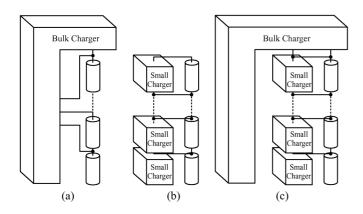

Batteries are an essential component of most electrically powered environment friendly applications. Given the TSMC 0.25  $\mu$ m bipolar-CMOS-DMOS (BCD) HV process, high voltage battery chargers capable of charging series connected batteries can be built using only integrated circuits and passive components. Basically, battery charger topologies used to charge series connected batteries can be sorted into three categories. These topologies include a bulk charger that charge all the batteries, a series of small chargers that independently charge their respective batteries, or a combination of both, as illustrated in Fig. 2 [6]. To take full advantage of the HV tolerance offered by this process, the bulk charger topology is

Manuscript received May 24, 2011; revised August 15, 2011; accepted October 26, 2011. Date of publication January 16, 2012; date of current version June 22, 2012. This work was supported in part by the National Science Council under Grant NSC 99-2221-E-110-082-MY3, Grant NSC 99-220-E-110-001, Grant NSC 99-2923-E-110-002-MY2, and Grant EZ-10-09-44-98, and in part by Ministry of Economic Affairs, Taiwan, under Grant 99-EC-17-A-01-S1-104 and Grant 99-EC-17-A-19-S1-133. This paper was recommended by Associate Editor E. Alarcon.

Fig. 2. (a) Bulk charger. (b) Small chargers. (c) Combination of both.

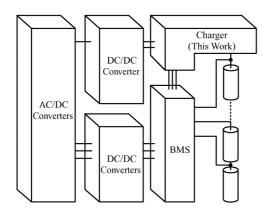

Fig. 3. Architecture of the battery charger.

selected for exemplification. Although balanced charging by the bulk charger is not inherently achieved without a series of small chargers, it can be easily enhanced with the inclusion of a battery management system (BMS) chip which actively balance and redistribute energy among the batteries. A complete embodiment of the system shown in Fig. 3 would also take advantage of ac/dc and dc/dc converters to provide a variable voltage corresponding to the battery voltage to the charger so that high charging efficiency can be achieved throughout the charging sequence [7].

This study is mainly focused on the design of the bulk charger, which is made capable of operating in both constant current (CC) mode and constant voltage (CV) mode. The bulk charger also supports a newly proposed incremental current (IC) mode, which is dedicated for economic integrated circuit packaging where a high parasitic inductance is included in the charging path. Section II serves as a quick introduction to the characteristics and limitation of the devices available to the HV process used to carry out this design. Conventional charging strategies and the associated problems regarding mode transition is also elucidated. Our system embodiment and the proposed charging sequence are covered in Section III. In Section IV, the analysis of circuits that is used to implement the bulk charger is presented. Notably, a solution that removes the stringent transistor sizing requirement imposed by the prevention of antenna effect is also revealed in this section. Experimental results are evaluated and compared with simulation results in Section IV.

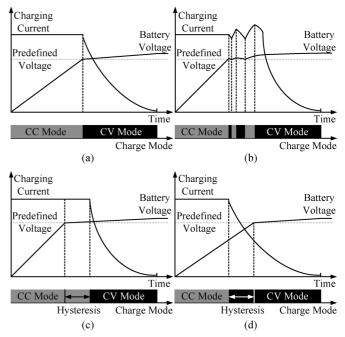

Fig. 4. (a) Current and voltage characteristics of an ideal CC/CV charger. (b) An unstable charger with oscillation between CC and CV modes. (c) A charger with positive hysteresis. (d) Negative hysteresis.

#### II. COMPARISON OF CHARGING STRATEGIES

When the voltage of the battery is low, a conventional battery charger starts the charging sequence by sourcing a regulated current to the battery, which is well known as the constant current (CC) mode. When the battery voltage rises, its internal ESR also increases. The battery charger is then switched into the constant voltage (CV) mode as soon as the battery voltage reaches a predefined level, where the charging voltage of the battery is regulated. When the battery voltage reaches the designated voltage level, the charging sequence is terminated. This charging strategy depicted in Fig. 4(a) is popularly regarded as the constant-current/constant-voltage (CC/CV) technique, which has been widely used in prior literature [7], [9]-[22]. However, straightforward implementation of the CC/CV technique using a voltage comparator can result in a potential stability problem during charge mode transition. As conceptually shown in Fig. 4(b), the charger switches from CC mode to CV mode as the feedback voltage from the battery becomes larger than the predefined reference voltage. An abrupt change of the charging current on the parasitic resistance causes a sudden voltage drop on the charging path from the charger to the battery, which in turn causes the sensed feedback voltage to drop. Consequently, the predefined reference voltage has a larger voltage value in comparison, and the charger is switched back to CC mode [10]. This kind of back-and-forth transitions can occur for an indefinite number of times during the entire charging sequence.

An apparent solution is to add hysteresis to the comparator to squelch the unstable rapid transitions between CC and CV modes, as demonstrated in Fig. 4(c) and (d). However, it is not easy to define an appropriate range of the hysteresis. Assume that the feedback voltage is connected to the positive node of

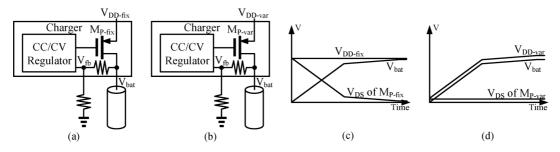

Fig. 5. Chargers with: (a) fixed and (b) variable supply voltage, and their conceptual voltages throughout the charge sequence (c), (d).

Fig. 6. A dc/dc converter controlled by the variable voltage regulator provides an appropriate variable supply voltage to a charger.

the comparator and the predefined voltage is coupled to the negative input of the comparator. Potential overheating of the battery may occur if the positive hysteresis range is made too large, delaying the entrance to CV mode. [12]. By contrast, if the negative hysteresis is used and the range is made too large, it will cause the battery charger to enter CV mode prematurely. Finally, if the hysteresis range is made too small, the rapid oscillation may still occur [10].

In Fig. 5(a), a charger consisting of a power MOS  $M_{P-fix}$ and a CC/CV regulator starts its charging sequence in CC mode. Since the battery is uncharged, the voltage node at V<sub>bat</sub> is at a low voltage value and the drop-out voltage  $V_{DS}$  across the transistor  $M_{P-fix}$  is as high as the voltage difference between V<sub>DD-fix</sub> and V<sub>bat</sub>. V<sub>DS</sub> will become gradually smaller as the battery is charged and V<sub>bat</sub> increases. However, since the charger charges the battery by regulating a high current to the battery in CC mode, the charging current will also flow directly through  $M_{P-fix}$  and cause a significant power loss on  $M_{P-fix}$ . Thus, such chargers are only capable of providing an inherently low charging efficiency. Heat dissipation can be another serious issue as well. The charger has different cooling requirement throughout the charging sequence, which must be accounted for the worst case when most power are dissipated across the transistor M<sub>P-fix</sub>. Therefore, economic packaging, e.g., side-brazed dual in-line packages, cannot meet the cooling constraint imposed by such chargers. By contrast, the charger shown in Fig. 5(b) is supplied by a variable supply voltage, V<sub>DD-var</sub>. This supply voltage is intended to track and provide a voltage slightly higher than  $V_{bat}$ . Hence, the drop-out voltage  $V_{\rm DS}$  across the transistor  $M_{\rm P-fix}$  is maintained at a predefined value such that the charging efficiency is significantly improved in the CC mode [7], [9], [12], [17]. The cooling requirement of such chargers in CC mode is also made less stringent as well.

The main overhead of implementing such a charger would be the need for an additional dc/dc converter, and the overall efficiency will also be affected by the efficiency of the dc/dc converter.

## III. PROPOSED CHARGING STRATEGY

## A. Embodiment of the Battery Charging Solution

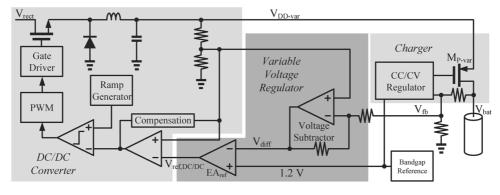

As depicted in Fig. 2, a complete battery charging system usually include a BMS, ac/dc converters, dc/dc converters, and a bulk charger [6]. The BMS is in charge of balancing the serially connected Li-ion batteries. The ac/dc converter is used to provide a rectified dc voltage, denoting as  $V_{\rm rect}$  in Fig. 6, to the dc/dc converters. DC/DC converters with fixed output voltage are used to provide power for both the controller circuits of the charger and the BMS, and an independent dc/dc converter (depicted in Fig. 6) is used to provide a variable voltage,  $V_{\rm DD-var}$ , for the charger.

The generation of a variable voltage can be understood by inspecting Fig. 6. First of all, a voltage subtractor is used to subtract the difference between the feedback voltage of the charger and dc/dc converter to generate a value  $V_{\rm diff}$ , which represents the voltage difference between  $V_{\rm DD-var}$  and  $V_{\rm bat}$ . An error amplifier,  $EA_{\rm ref}$ , regulates  $V_{\rm diff}$  to a bandgap reference voltage value of 1.2 V by adjusting  $V_{\rm ref,dc/dc}$ , which serves as a variable reference voltage for the dc/dc converter. Finally, by using pulse width modulation (or any other appropriate modulation), the variable voltage is generated. Since charging operation is considerably slower than the dynamic response of the dc/dc converter, it would be unnecessary for the dc/dc converter to be designed with fast reference tracking capability.

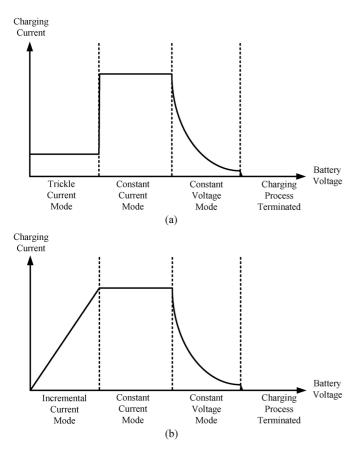

Fig. 7. The relationship of charging current against battery voltage for a battery charger with: (a) trickle current mode, and (b) incremental current mode. Note that the XY axis of this figure differs from that of Fig. 5.

Fig. 8. The aftermath of inductive kickback. Both the bond-wires and the bond pads are permanently damaged.

## *B. Incremental Current, Constant Current, and Constant Voltage Modes*

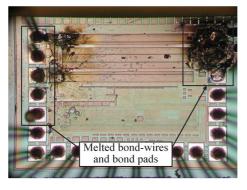

During the initial charging sequence, it may be inappropriate to charge deeply uncharged batteries with a high current. The trickle current (TC) mode [7] can resolve this problem by sourcing a smaller current to the battery, and switch to CC mode when the battery voltage reaches a predefined value, as shown in Fig. 7(a). In practical scenarios, the charger circuit fabricated on a chip must be packaged, thereby introducing parasitic inductance on the bond-wires with a value ranging from 1 nH to 3 nH on the charging path. The parasitic inductance depends on the length of the bond-wires, which cannot be easily estimated before the chip is packaged. If both the parasitic inductance and the charge current are large enough, a sudden switch from the TC mode to the CC mode will result in an inductive kickback, melting both the bond-wires and the connected pads, as shown in Fig. 9. To prevent such catastrophes, the TC mode is modified into the incremental current (IC) mode, as shown in Fig. 7(b). The charging current becomes a function of the battery voltage. More specifically, the charging current increases gradually as the battery voltage increases. However, this charging current does not increase unlimitedly. It is clamped at a predefined value, which the charger enters the CC mode without a discontinuous transition with respect to the charging current.

## **IV. CIRCUIT IMPLEMENTATION**

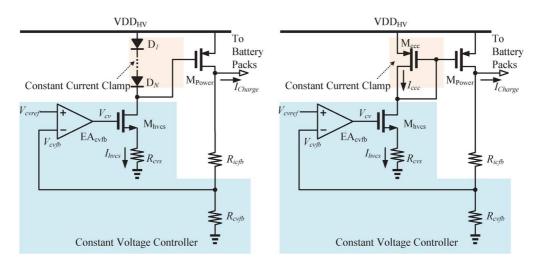

## A. Constant Voltage Loop and Diode-Based Constant Current Clamp

As depicted earlier in Fig. 5, there can be problems switching from CC and CV mode. Apparently, smooth charge mode transition between CC to CV modes is essential to the stability of a charger. To elegantly resolve this problem, the CV regulating loop should be able to clamp the maximum output charging current. In other words, the CC and CV feedback loops are combined into one, which has been reported in [12]. As shown in Fig. 9(a), this scheme consists of a linear dropout regulator (LDO)-like constant voltage controller and a series of diodes  $D_1$  to  $D_N$ , where N is the number of diodes. In CV mode, the charger behaves analogously to a typical LDO. An error amplifier,  $EA_{cvfb}$ , is used to generate an error voltage,  $V_{cv}$ , based on the difference of the shunt-feedback battery voltage  $V_{\rm cvfb}$  and the reference voltage  $V_{\rm cvref}$ .  $V_{\rm cvref}$  is responsible of driving the cascaded level shifter which in turn biases the power  $MOS M_{Power}$  is driven by the level shifter so that an appropriate amount of current is regulated into the battery.

In situations when  $V_{\text{cvfb}}$  is far lower than the predefined  $V_{\text{cvref}}, V_{\text{cv}}$  is pulled up close to the supply voltage of  $\text{EA}_{\text{cvfb}}$ , and  $M_{\text{hvcs}}$  will attempt to pull the gate of  $M_{\text{Power}}$  all the way to ground. However, since  $M_{\text{hvcs}}$  is designed with the minimum width and long length in dimension, and it is also source-degenerated with  $R_{\text{cvs}}$ , its current sinking ability is limited. Hence, the diodes  $D_1$  to  $D_N$  will clamp the gate of  $M_{\text{Power}}$  at a value of  $V_{\text{Clamp}}$  lower than  $\text{VDD}_{\text{HV}}$ . This can ensure that the maximum value of  $I_{\text{Charge}}$  is limited to a finite value governed by

$$I_{\text{Charge}} = \frac{1}{2} K'_p \frac{W}{L} (V_{\text{Clamp}} - V_{\text{thp}})^2$$

$$= \frac{1}{2} K'_p \frac{W}{L} (N \times V_{Don} - V_{\text{thp}})^2.$$

(1)

As revealed in (1), the absolute resistance value of  $R_{\rm cvs}$  does not affect the charging current, as long as the diodes can be turned on. The sensitivity of the charging current with respect to the voltage variation over the diode string is given as follows:

$$S_{N \times V_{\text{Don}} - V_{\text{thp}}}^{I_{\text{Charge}}} = \frac{\partial I_{\text{Charge}} / I_{\text{Charge}}}{\partial (N \times V_{\text{Don}} - V_{\text{thp}}) / (N \times V_{\text{Don}} - V_{\text{thp}})}$$

$$= \frac{\partial I_{\text{Charge}}}{\partial (N \times V_{\text{Don}} - V_{\text{thp}})} \times \frac{N \times V_{\text{Don}} - V_{\text{thp}}}{I_{\text{Charge}}}$$

$$= \frac{K_p' \frac{W}{L} (N \times V_{\text{Don}} - V_{\text{thp}})^2}{I_{\text{Charge}}}$$

$$= 2. \tag{2}$$

Fig. 9. (a) The constant voltage controller with diode-based constant current clamp [12]. (b) The constant voltage controller with diode-connected load as constant current clamp.

Fig. 10. (a) The nonlinear relationship between  $I_{\rm hvcs}$  and  $R_{\rm cvs}$ . (b) The nonlinear relationship between  $I_{\rm hvcs}$  and temperature.

This indicates that the charging current  $I_{\rm Charge}$  is sensitive to both  $V_{\rm Clamp}$  and  $V_{\rm thp}$  by a factor of 2. For example, if  $V_{\rm Clamp} - V_{\rm thp}$  is only 80% of the desired value (20% variation),  $I_{\rm Charge}$  becomes 64% of the anticipated maximum charging current (36% variation). Hence, the actual charging current will deviate greatly from simulation results. This also explains the low charging current and, consequently, the low efficiency of the charger proposed in [12].

## B. Constant Voltage Loop and Diode-Connected Load as Constant Current Clamp

To avoid such an undesired deviation, the voltage clamp should be made adjustable after the charger has been fabricated on silicon to account for process variation. Instead of placing serially connected diodes to clamp the voltage, a diode-connected power PMOS  $M_{\rm ccc}$  is used, as shown in Fig. 9(b). From the following equations:

$$V_{\rm cv} = V_{\rm gs,hvcs} + I_{\rm hvcs} \times R_{\rm cvs} = 5$$

(3)

$$I_{\rm ccc} = I_{\rm hvcs} = \frac{1}{2} K'_n \left(\frac{W}{L}\right) (V_{\rm gs,hvcs} - V_{\rm thn})^2 \qquad (4)$$

we attain

$$V_{\text{Clamp}} = \sqrt{\frac{10 - 2V_{\text{gs,hvcs}}}{R_{\text{cvs}} \times K'_p}} - V_{\text{thp}}$$

(5)

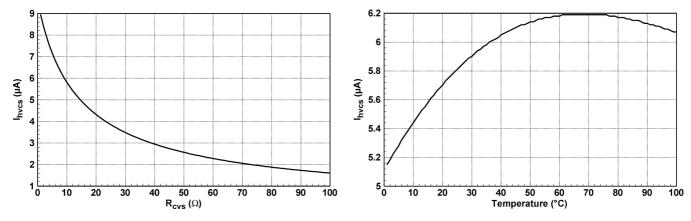

where  $V_{\rm gs,hvcs}$  is the gate-source voltage of  $M_{\rm hvcs}$ ,  $V_{\rm cv}$  is the gate voltage of  $M_{\rm hvcs}$  pulled up to the supply voltage value of 5 V, and 10 is two times of the 5 V supply voltage. Evidently, the maximum gate-source voltage  $V_{\rm Clamp}$  of  $M_{\rm ccc}$  and  $M_{\rm Power}$  is no longer a fixed value, but an adjustable voltage determined by the resistance value of  $R_{\rm cvs}$ . The nonlinear relationship between  $I_{\rm hvcs}$  and  $R_{\rm cvs}$  is plotted in Fig. 10(a).

This implementation can also be interpreted as a current mirror copying the current that flows through  $R_{\rm cvs}$ , multiplying the current by the aspect ratio of M<sub>Power</sub> vs. M<sub>ccc</sub>, and generating  $I_{\rm Charge}$  to charge the battery.

If an npn transistor is used in the place of  $M_{\rm hvcs},$  this equation becomes

$$V_{\text{Clamp}} = \sqrt{\frac{10 - 2V_{be}}{R_{\text{cvs}} \times K'_p}} - V_{\text{thp}} \approx \sqrt{\frac{8.6}{R_{\text{cvs}} \times K'_p}} - V_{\text{thp}}.$$

(6)

Since  $M_{Power}$  also shares the same  $V_{thp}$  and  $K'_p$  with  $M_{ccc}$ ,  $I_{Charge}$  becomes a clearly defined value with respect to  $R_{cvs}$ . Unfortunately, with the absence of an npn transistor with high  $\beta$  value in this process, this solution is currently unavailable.

Note that the resistance of  $R_{\rm cvs}$  is also a function of temperature, making  $I_{\rm Charge}$  temperature-dependent. The resistor value can be generally approximated by [23]

$$R(T) = R_0 \times \{1 + \text{TC1}\,\Delta T + \text{TC2}\,\Delta T^2\}$$

(7)

Fig. 11. The incremental current controller augmented to the constant voltage controller with diode-connected load as constant current clamp.

Fig. 12. The schematic of the V-to-I converter.

where TC1 and TC2 are temperature coefficients,  $R_0$  is the resistance measured at room temperature, and  $\Delta T$  is the difference between the temperature with the room temperature 25 °C. The nonlinear relationship between of  $I_{\text{Charge}}$  and temperature is plotted in Fig. 10(b) using a resistor of 10 k $\Omega$  with coefficients TC1 =  $10^{-2}$  and TC2 =  $10^{-4}$  as  $R_{\text{cvs}}$ .

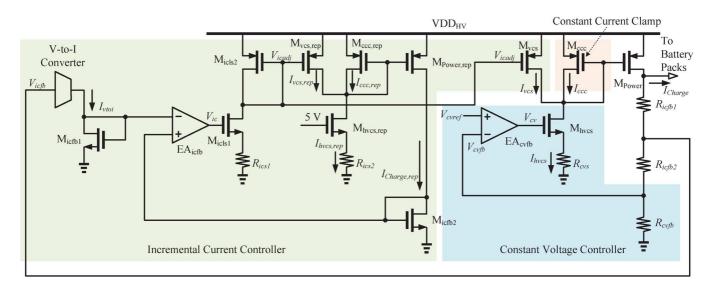

## C. Incremental Current Loop

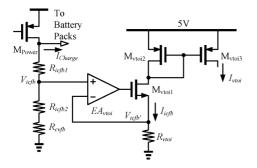

Fig. 11 shows the schematic of the incremental current controller augmented to the original CV controller. The V-to-I converter is responsible of generating a reference current,  $I_{vtoi}$ , corresponding to the contemporaneous battery voltage. As depicted in Fig. 12, the virtual-short characteristic of the error amplifier  $EA_{vtoi}$  causes the feedback voltage  $V_{icfb}$  to be copied to  $V_{icfb}$ . This in turn generates a current signal  $I_{icfb}$  that flows through both  $M_{vtoi1}$  and  $M_{vtoi2}$ .  $M_{vtoi3}$  copies  $I_{icfb'}$  and generates  $I_{vtoi}$ [24], which flows through  $M_{icfb1}$  to create a voltage signal at the negative node of the error amplifier  $EA_{icfb}$ .

By making  $M_{vtoi1}$  wide enough, we can obtain the transition voltage,  $V_{tr}$ , from IC mode to CC mode using the following relationships:

$$V_{\rm tr} = R_{\rm voti} \times I_{\rm icfb(max)} = 5 - V_{\rm vtoi2} - V_{\rm vtoi1} \qquad (8)$$

where 5 is the voltage supply,  $V_{\text{vtoi1}}$  is the overdrive voltage of  $M_{\text{vtoi2}}$ , and  $V_{\text{vtoi2}}$  is the gate-source voltage of  $M_{\text{vtoi2}}$ .

$V_{\rm vtoi1}$  and  $V_{\rm vtoi2}$  can be expressed as

I

$$V_{\text{vtoi1}} = \sqrt{\frac{2I_{\text{icfb}(\text{max})}}{K'_n \left(\frac{W}{L}\right)_{\text{vtoi1}}}} \tag{9}$$

$$V_{\rm vtoi2} = V_{\rm thp} + \sqrt{\frac{2I_{\rm icfb(max)}}{K'_p \left(\frac{W}{L}\right)_{\rm vtoi2}}} \tag{10}$$

where  $(W/L)_{vtoi1}$  and  $(W/L)_{vtoi2}$  are the aspect ratios of  $M_{vtoi1}$  and  $M_{vtoi2}$ , respectively. Hence,

$$V_{\rm tr} = 5 - \left[ V_{\rm thp} + \sqrt{\frac{2I_{\rm icfb}(\max)}{K'_n \left(\frac{W}{L}\right)_{\rm vtoi1}}} + \sqrt{\frac{2I_{\rm icfb}(\max)}{K'_p \left(\frac{W}{L}\right)_{\rm vtoi2}}} \right]$$

(11)

By using some algebraic manipulation, we obtain

$$V_{\rm tr} = \sqrt{\frac{1}{\alpha^2} - 5 + V_{\rm thp}} - \frac{1}{\alpha} \tag{12}$$

where

$$\alpha = \frac{R_{\text{vtoi}}}{2\sqrt{2}} \times \left[ \sqrt{K'_n \left(\frac{W}{L}\right)_{\text{vtoi1}}} + \sqrt{K'_p \left(\frac{W}{L}\right)_{\text{vtoi2}}} \right].$$

(13)

If  $M_{vtoi1}$  is narrow,  $V_{tr}$  will be limited by  $5 - V_{thn'}$ . Note that due to body effect,  $V_{thn'}$  will be significantly larger than  $V_{thn}$ . Hence, the mode transition voltage,  $V_{tr}$ , can be defined as

$$V_{\rm tr} = min\left[\left(5 - V_{\rm thn'}\right), \left(\sqrt{\frac{1}{\alpha^2} - 5 + V_{\rm thp}} - \frac{1}{\alpha}\right)\right].$$

(14)

Direct sensing of  $I_{\text{Charge}}$  to attain a precise current signal requires the addition of a current sensing resistor, which degrades efficiency significantly when the charging current is high. Instead, a replica circuit consisting of  $M_{\text{hvcs,rep}}$ ,  $M_{\text{ccc,rep}}$ ,  $M_{\text{Power,rep}}$ , and  $R_{\text{ics2}}$  is used to generate  $I_{Charge,rep}$ , which is a fractionized  $I_{\text{Charge}}$ . The gate of  $M_{\text{hvcs,rep}}$  is connected to the voltage supply, mimicking  $V_{\text{cv}}$  which is also pulled to the voltage supply by  $\text{EA}_{\text{cvfb}}$  before the charger enters CV mode. It is worth noting that the gate of  $M_{\text{hvcs,rep}}$  must be connected to the supply voltage internally, since N-type LDMOS transistors are susceptible to ESD [25]. The value of  $R_{\text{ics2}}$  should be made close to  $R_{\rm cvs}$ , but direct matching between the two is unnecessary. The mismatch between the two resistance will only cause negligible effect on  $I_{\rm Charge,rep}$  during IC mode.

$EA_{icfb}$  indirectly drives  $M_{vcs,rep}$  through  $M_{icls1}$  and  $M_{icls2}$ to steal current  $I_{vcs,rep}$  from  $I_{ccc,rep}$ , which is the drain current of  $M_{ccc,rep}$ . Consequently,  $I_{Charge,rep}$  flowing through  $M_{Power,rep}$  and  $M_{icfb2}$  is scaled proportionally to  $I_{ccc,rep}$ .  $EA_{icfb}$  regulates the voltage generated by  $I_{Charge,rep}$  to the voltage generated by  $I_{vtoi}$ , which simultaneously regulates the current  $I_{Charge,rep}$  itself to  $I_{vtoi}$ . Since the gate of  $M_{vcs}$  and  $M_{vcs,rep}$  are driven by the same voltage,  $V_{icadj}$ , the amount of current  $I_{vcs}$  stolen from  $I_{ccc}$  will be proportional to the amount  $I_{vcs,rep}$  stolen from  $I_{ccc,rep}$ . Hence,  $I_{Charge}$  will be proportional to  $I_{Charge,rep}$ , which in turn is proportional to the feedback voltage,  $V_{icfb}$ .

Throughout the charging sequences, the IC loop and the CV loop do not interact with each other. Whenever a loop is controlling the behavior of the charger, the other loop is saturated such that it cannot affect the operation of the charger. Hence, stability issues are dramatically simplified and smooth transition between charge modes is ensured regardless of what mode the charger is.

## D. Antenna Effect Protection Pad

The antenna effect, more formally known as the plasma induced gate oxide damage, can potentially damage integrated circuits during the manufacture process [27]-[31]. Such an effect occurs when the metal connected to the gate of a MOS transistor somehow acquires a voltage higher than the maximum sustainable voltage of that transistor during fabrication. Since the gate dielectric is only a few molecules thin, breakdown may occur [31]. Furthermore, if an input transistor of a differential pair is subject to the plasma induced gate oxide damage, an offset voltage is induced [32] and the overall system closed-loop accuracy is degraded. To prevent plasma induced gate oxide damage, foundries often provide antenna rules based on antenna ratio, AR, which is the allowable ratio of metal area to gate area. The definition of AR can be found in [33], [34]. However, since the ultra-thick top metal (UTM) thickness of this process is 30 kÅ (3  $\mu m$ ) [8], the height of both the metal and the polysilicon should be taken into account:

$$AR = \frac{\kappa(W_M \times L_M \times H_M)}{W_P \times L_P \times H_P}$$

(15)

where  $W_M$ ,  $L_M$ ,  $H_M$  are the width, length, and height of the metal, respectively.  $W_P$ ,  $L_M$ , and  $M_P$  are the width, length, and height of the polysilicon of the MOS transistor connected to the metal.  $\kappa$  is a coefficient.

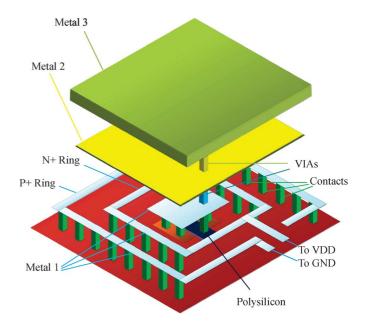

A bonding PAD typically consumes an area of  $70 \ \mu m \times 80 \ \mu m$ on all three metal layers. Hence, transistors with their gate node connected to bonding pads must be large enough to meet the minimum AR requirements. Unfortunately, such requirements restrict the user from connecting an external node to small transistors such that unnecessary dilemmas regarding the selection of transistor aspect ratios may appear. To resolve this issue, the proposed antenna effect protection pads can be deployed instead of standard pads. The antenna effect protection PAD is obtained by adding a dummy 0.5  $\mu m$  PMOS transistor beneath the stan-

Fig. 13. The antenna effect protection PAD.

dard PAD, as shown in Fig. 13. Notably, both drain and source of the PMOS transistors are coupled to Metal 1 (M1) using contacts. The drain and source node can provide forward diode connection when a voltage is higher than 5 V appears on any metal layers so that the gate oxide of the connected small transistors is protected. The isolation rings are connected to ground and the 5 V supply voltage, respectively. Since the N-well is also connected to the 5 V supply voltage and drain/source are shorted together, high dc impedance is achieved. Parasitic capacitance existing between bulk and the other three shorted terminals is at its minimum value, since the PMOS is in cut-off region. Hence, antenna effect protection pads have negligible impact on circuit behavior while providing adequate protection to meet the AR requirements set by foundries. The parasitic capacitance can be estimated as [35]

$$C_{\text{pad}} \approx \varepsilon_{\text{ox}} \left[ 1.15 \times \frac{A_{\text{pad}}}{h} + 1.4 \times p_{\text{pad}} \times \left(\frac{t}{h}\right)^{0.222} \right]$$

(16)

where  $A_{pad}$ ,  $p_{pad}$  and t are the area, periphery, and thickness of the antenna effect protection pad, respectively. h is the distance of the bottom metal plate to the substrate, and  $\epsilon_{ox}$  is the dielectric constant of SiO<sub>2</sub>. Since the M1 layer is removed, h is increased and the total parasitic capacitance is reduced.

Finally, since antenna effect protection pads do not require additional silicon area, they can be placed without increasing the total layout cost of the chip.

## V. EXPERIMENTAL RESULTS

To evaluate the charging current with respect to the battery voltage, the targeted battery load of  $14 \times 4.2$  V Li-ion batteries are emulated with Prodigi 3311D programmable dc electronic load, and the variable voltage is supplied by a Chroma 62012p-600-8 programmable power supply.

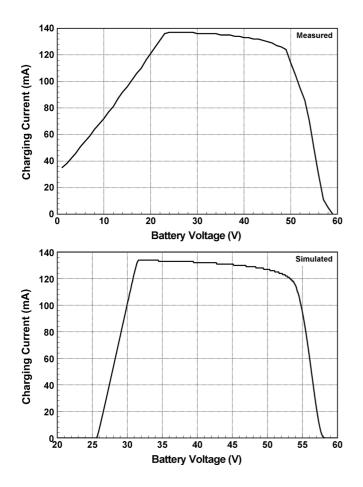

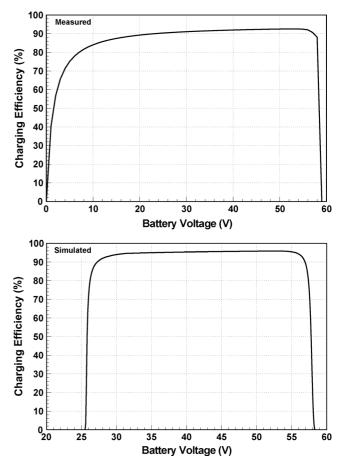

As shown in Fig. 14, the charger begins with a charging current of 36 mA, which slowly rises to 136 mA. To improve efficiency, resistor  $R_{\rm cvs}$  is increased to 20 k $\Omega$  instead of the value

Fig. 14. Measured charging current and simulated charging current of the charger as a function of the battery voltage.

14.5 k $\Omega$  used in simulation. It has caused an impact on the characteristics of the charger in IC mode, but it is possible to remove the deviation if  $R_{ics2}$  is also connected externally and made equal to  $R_{cvs}$ . These results are tolerable, since they only interfere with the initial charge sequence of the batteries. IC mode neither determines when the battery transits from CC mode to CV mode nor decides when the charge sequence ends. Charging efficiency with respect to the battery voltage is plotted in Fig. 15. This charger has a peak efficiency up to 92% during the charging sequence. Notably, even a deeply uncharged 4.2 V battery may still have more than 2 V such that a series of 14 batteries should at least have a voltage of 28 V. Therefore, the simulated low efficiency below 26 V shown in Fig. 15 would never occur in practical scenario.

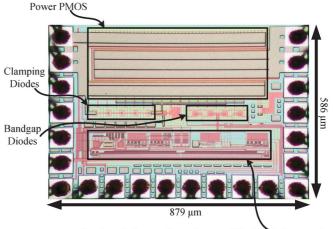

The proposed chargers have been fabricated using TSMC 0.25  $\mu$ m BCD 60 V technology. The chip shown in Fig. 16 was proposed in [12]. It features diode-based constant current clamp, which has a high sensitivity to process and temperature variation. The TC mode of this charger is unusable, since an inductive kickback it induces permanently damages the charger occurs when triggered. It occupies a total silicon area of  $586 \times 879 \,\mu$ m<sup>2</sup> (with pads).

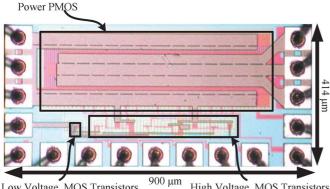

The TC mode has been replaced with IC mode in the chip shown in Fig. 17. Unlike its earlier counterpart which used low voltage transistors with long lengths, feature-sized transistors were used instead. This greatly reduces silicon area occupied

Fig. 15. Measured charging efficiency and simulated charging efficiency of the charger as a function of the battery voltage.

Bandgap Reference, Error Amp, and Hysteresis Comparator

Fig. 16. The die photo of the charger with bandgap reference, hysteresis comparators, and diode-based constant current clamp.

by low voltage (LV) circuits. Since this charger is intended to be integrated into a complete BMS solution in the future,  $V_{\rm cvref}$ is made to be adjustable so that bypassing batteries from the charging path can be achieved. Hence, the bandgap reference is removed so that  $V_{\rm cvref}$  can be adjusted directly using a digital-to-analog converter (DAC). This charger occupies a total silicon area of 414 × 900  $\mu$ m<sup>2</sup> (with pads).

High Voltage MOS Transistors Low Voltage MOS Transistors

Fig. 17. The die photo of the charger supporting IC/CC/CV charge modes.

|                                | [12]                       | This Work                  |

|--------------------------------|----------------------------|----------------------------|

| Supply Voltage                 | 60 V                       | 60 V                       |

| Maximum Charge<br>Current      | 52 mA                      | 136 mA                     |

| Peak Efficiency                | 80 %                       | 92 %                       |

| Supported                      | CC Mode                    | CC Mode                    |

| Charge Modes                   | CV Mode                    | CV Mode                    |

| 88                             | TC Mode $(\times)$         | IC Mode                    |

| Over Temperature<br>Protection | Yes                        | No                         |

| Antenna Effect<br>Protection   | No                         | Yes                        |

| Silicon Area                   | $586 \times 879 \ \mu m^2$ | $414 \times 900 \ \mu m^2$ |

| Year                           | 2011                       | 2012                       |

TABLE I CHARGER COMPARISON

(x) Denotes not functional.

Finally, a comparison of these two chargers is tabulated in Table I. Since TC mode is not functional, it is denoted with a " ×" symbol.

## VI. CONCLUSION

A 60-V high voltage charger capable of charging 14 serially connected 4.2-V lithium-ion batteries with smooth charge mode transition is presented along with measured results. The circuit combines two different regulation loops into a single circuit with smooth transition between different modes. High efficiency is achieved by sourcing a variable voltage supply that tracks the voltage of the batteries to reduce unwanted power dissipation. This design is carried out using the TSMC 0.25  $\mu m$ BCD 60-V technology.

#### ACKNOWLEDGMENT

The authors would like to express their gratitude toward Chip Implementation Center (CIC), Taiwan, the organization that maintained Taiwan's superiority in academic integrated circuit design capability for the past decade, and several remarkable individuals, namely, Tsai Hui Han, Chang Wen Shu, Hsieh Yuan Da, and Fang Chiao Li, for their support over the the TSMC Bipolar-CMOS-DMOS (BCD) 0.25  $\mu m$  process to the authors and other academic users of Taiwan.

## REFERENCES

- [1] Power MOSFET Wikipedia [Online]. Available: http://en.wikipedia. org/wiki/Power\_MOSFET

- [2] C.-H. Tsai, Class notes, 'Power Management Integrated Circuits,' offered at National Cheng-Kung University, Tainan, Taiwan, 2009

- [3] Y. Tan, M. Kumar, J. K. O. Sin, J. Cai, and J. Lau, "A LDMOS technology compatible with CMOS and passive components for integrated RF power amplifiers," IEEE Electron Device Lett., vol. 21, no. 2, pp. 82-84, Feb. 2000.

- [4] High Voltage and Power Management Technology, Taiwan Semiconductor Manufacturing Company [Online]. Available: http://www.tsmc. com/english/newsEvents/dc brochure.htm

- [5] Process Introduction, Chip Implementation Center [Online]. Available: http://www.cic.org.tw/cic\_v13/fab\_services/index.jsp?menu=intro

- [6] D. Andrea, Battery Management Systems for Large Lithium-Ion Battery Packs. Norwood, MA: Artech House, 2010.

- [7] J.-J. Chen, F.-C. Yang, C.-C. Lai, Y.-S. Hwang, and R.-G. Lee, "A high-efficiency multimode Li-ion battery charger with variable current source and controlling previous-stage supply voltage," IEEE Trans. Ind. Electron., vol. 56, no. 7, pp. 2469-2478, Jul. 2009.

- [8] Notes to Tape-Out Related Applications, Chip Implementation Center, pp. 20-22 [Online]. Available: http://www2.cic.org.tw/~cis/chipapply/ doc/handout.pdf

- [9] M. Chen and G. A. Rincon-Mora, "Accurate, compact, and power-efficient Li-ion battery charger circuit," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 11, pp. 1180-1184, Nov. 2006.

- [10] C.-H. Lin, C.-Y. Hsieh, and K.-H. Chen, "A Li-ion battery charger with smooth control circuit and built-in resistance compensator for achieving stable and fast charging," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 2, pp. 506-517, Feb. 2010.

- [11] Y.-S. Hwang, S.-C. Wang, F.-C. Yang, and J.-J. Chen, "New compact CMOS Li-Ion battery charger using charge-pump technique for portable applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 54, no. 4, pp. 705-712, Apr. 2007.

- [12] S.-H. Yang, J.-W. Liu, Y.-H. Wu, D.-S. Wang, and C.-C. Wang, "A high voltage battery charger with smooth charge mode transition in BCD process," in Proc. IEEE ISCAS, May 2011, pp. 813-816.

- [13] Single-Cell Li-Ion Charge Management IC for PDAs and Internet Appliances, Texas Instruments, 2004 [Online]. Available: http://focus.ti. com/lit/ds/symlink/bq24001.pdf

- [14] Two-Cell Li-Ion Charge Management IC for PDAs and Internet Appliances, Texas Instruments, 2005 [Online]. Available: http://focus.ti. com/lit/ds/symlink/bq24004.pdf

- [15] Lithium Ion Fast-Charge IC, Texas Instruments, 2009 [Online]. Available: http://focus.ti.com/lit/ds/symlink/bq2054.pdf

- [16] Lithium Ion Charge Management IC With Integrated Switching Controller, Texas Instruments, 2010 [Online]. Available: http://focus.ti. com/lit/ds/symlink/bq2954.pdf

- [17] Standalone Linear Li-Ion Battery Charger and Dual Synchronous Buck Converter, Linear Technology, 2006 [Online]. Available: http://cds.linear.com/docs/Datasheet/3552f.pdf

- [18] Standalone Linear Li-Ion Battery Charger With Thermal Regulation in DFN, Linear Technology, 2004 [Online]. Available: http://cds.linear. com/docs/Datasheet/405842fs.pdf

- [19] Dual Input USB/AC Adapter Standalone Li-Ion Battery Chargers, Linear Technology, 2006 [Online]. Available: http://cds.linear.com/ docs/Datasheet/4075Xfa.pdf

- [20] Linear Charger for Single-Cell Li+ Battery, Maxim, 2002 [Online]. Available: http://datasheets.maxim-ic.com/en/ds/MAX1898.pdf

- [21] Single-Cell Li+ Battery Charger for Current-Limited Supply, Maxim, 2000 [Online]. Available: http://datasheets.maxim-ic.com/en/ds/ MAX1679.pdf

- [22] 1.5 A Dual-Input USB/AC Adapter Charger and Smart Power Selector, Maxim, 2011 [Online]. Available: http://datasheets.maxim-ic. com/en/ds/MAX8677C.pdf

- [23] T. Quarles, A. R. Newton, D. O. Pederson, and A. Sangiovanni-Vincentelli, SPICE3 Version 3f3 User's Manual, Univ. California. Berkeley, CA, 1993 [Online]. Available: http://bwrc.eecs.berkeley.edu/Classes/ IcBook/SPICE/

- [24] W. Sansen, Analog Design Essentials. Berlin, Germany: Springer, 2006, p. 381.

- [25] W.-Y. Chen and M.-D. Ker, "Circuit and layout co-design for ESD protection in bipolar-CMOS-DMOS (BCD) high-voltage process," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 5, pp. 1039-1047, May 2010

- [26] J. Baker, CMOS Circuit Design, Layout, and Simulation, 2nd Ed.. Hoboken, NJ: Wiley, 2008, p. 914.

- [27] T. Watanabe and Y. Yoshida, "Dielectric breakdown of gate insulator due to reactive etching," *Solid State Technol.*, vol. 26, no. 4, p. 263, Apr. 1984.

- [28] C. Gabriel and J. McVittie, "How plasma etching damages thin gate oxides," *Solid State Technol.*, vol. 34, no. 6, p. 81, Apr. 1992.

- [29] S. Fang and J. McVittie, "Thin-oxide damage from gate charging during plasma processing," *IEEE Electron Device Lett.*, vol. 13, no. 5, p. 288, Feb. 1992.

- [30] H.-C. Shin and C.-M. Hu, "Thin gate oxide damage due to plasma processing," *Semicond. Sci. Technol.*, vol. 11, pp. 463–473, Nov. 1996.

- [31] Antenna Effect, Wikipedia [Online]. Available: http://en.wikipedia. org/wiki/Antenna effect

- [32] H.-C. Shin, C. C. King, and C.-M. Hu, "Thin oxide damage by plasma etching and ashing processes," in *Proc. IEEE Int. Rel. Phys. Symp.*, Apr. 1992, p. 37.

- [33] J. Liobe, "The antenna effect: Problem and solutions,". Technion, Israel, 2004 [Online]. Available: http://webee.technion.ac.il/ courses/048864/rochester/spring%202004%20presentations/465\_antenna%20effects.pdf

- [34] Z. Chen and I. Koren, "Layer reassignment for antenna effect minimization in 3-layer channel routing," in *Proc. IEEE Int. Symp. Defect Fault Tolerance VLSI Syst.*, Nov. 1996, pp. 77–85.

- [35] K. Martin, Digital Integrated Circuit Design. London, U.K.: Oxford Univ. Press, 1999.

**Shang-Hsien Yang** (S'09) received the B.Sc. and M.S. degrees in electrical engineering from National Sun Yat-Sen University, Taiwan, in 2009 and 2011, respectively.

Since September 2011, he has been serving his national service for the Ministry of Foreign Affairs, Taiwan. During 2010 to 2011, he was elected the Chairperson of IEEE Student Branch both at NSYSU and Tainan Section. He was also nominated as the graduate student representative at the department of electrical engineering, NSYSU from 2009 to 2011.

His research interest includes power management integrated circuits.

Jen-Wei Liu received the B.Sc. and M.S. degree in electrical engineering from National Sun Yat-Sen University, Taiwan, in 2008 and 2010, respectively. He is currently with Etron Technology, Inc. His research interests includes level-shifting I/O interface for multiple voltage systems.

**Chua-Chin Wang** (M'90–SM'04) received the Ph.D. degree in electrical engineering from State University of New York (SUNY), Stony Brook, in 1992.

He then joined the Department of Electrical Engineering, National Sun Yat-Sen University, Taiwan, and became a full Professor in 1998. He founded the SOC group in the Department of Electrical Engineering, National Sun Yat-Sen University, in 2005. He is currently Chairman of this department. He co-founded Asuka Semiconductor Inc., which is

an IC design house located in renowned Hsinchu Scientific Park, Taiwan, and became Executive Secretary in 2005. His research interests include memory and logic circuit design, communication circuit design, neural networks, and interfacing I/O circuits. Particularly, he applies most of his research results on biomedical, memories, consumer electronics, and wireless communication applications, such as implantable ASIC/SOC, DVB-T/H, and NTSC TV circuits, low power memory, high speed digital logic, etc.

Prof. Wang has won the Outstanding Youth Engineer Award of Chinese Engineer Association in 1999, and NSC Research Award from 1994 to 1999. In 2000. In 2005, he was awarded with Best Inventor Award in National Sun Yat-Sen University, Taiwan. In 2006, he won "Distinguished Engineering Professor" Award of Chinese Institute of Engineers and "Distinguished Engineer" Award of Chinese Institute of Electrical Engineering in the same year. He also won Distinguished Electrical Engineering Professor Award of Chinese Institute of Electrical Engineers in 2007. In 2008, he won Outstanding Paper Award of 2008 IEEE Inter. Conf. of Consumer Electronics. In 2009, he again won Best Inventor Award. He was Chair of IEEE Circuits and Systems Society (CASS) for 2007 2008, Tainan Chapter. He was also the founding Chair of IEEE Solid-State Circuits Society (SSCS), Tainan Chapter for 2007 2008, and the founding Consultant of IEEE NSYSU Student Branch. He is also a member of the IEEE CASS Multimedia Systems & Applications (MSA), VLSI Systems and Applications (VSA), Nanoelectronics and Giga-scale Systems (NG), and Biomedical Circuits and Systems (BioCAS) Technical Committees. In 2007, he was elected to be Chair-elect of IEEE CASS Nanoelectronics and Giga-scale Systems (NG) Technical Committee to serve a 2-year term of 2008 2009. Since 2010, he has been an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS PARTS I and II. Currently, he is also serving as Associate Editor of IEICE Transactions on Electronics, and Journal of Signal Processing. He was General Chair of 2007 VLSI/CAD Symposium. He was General Co-Chair of 2010 IEEE International Symposium on Next-generation Electronics (2010 ISNE). He is General Chair of 2011 IEEE International Conference on IC Design and Technology (2011 ICICDT), and General Chair of 2012 IEEE Asia-Pacific Conference on Circuits and Systems (2012 APCCAS).