# A 60 V Tolerance Transceiver With ESD Protection for FlexRay-Based Communication Systems

Chua-Chin Wang, Chih-Lin Chen, Zong-You Hou, Yi Hu, Jam-Wem Lee, Wan-Yen Lin, Yi-Feng Chang, Chia-Wei Hsu, and Ming-Hsiang Song

Abstract—In this paper, a 60 V tolerance transceiver with ESD (electrostatic discharge) protection is proposed for FlexRay-based communication systems. The FlexRay transceiver comprises three protective devices, including an over-voltage detector, high-voltage ESD devices, and high-voltage diodes. The over-voltage detector is in charge of detecting bus (BP and BM) status to distinguish whether any hazard has happened. If the over-voltage detector is activated, the FlexRay transceiver must be turned off for safety. The high-voltage ESD device uses a base-floating PNP serving as a bi-directional device. Besides, it can protect the FlexRay transceiver whenever it is short-circuited in positive or negative high voltages. Notably, the high-voltage diode will eliminate the negative leakage current when negative high voltage hazards appear in FlexRay channels. An experimental prototype is implemented using a 0.18  $\mu$ m CMOS mixed-signal based generation II HV BCD process. The measurement results justify the functional correctness and 60 V tolerance of the proposed FlexRay transceiver design.

*Index Terms*—FlexRay transceiver, high-voltage diode, high-voltage ESD device, over-voltage detector.

## I. INTRODUCTION

**T** N RECENT years, in-vehicle systems on silicon became very nonular due to the second state of the secon came very popular due to the evolution of semiconductor technology [1], [2]. This trend will become more dominating when high voltage technologies are affordable, e.g., Bipolar/CMOS/DMOS (BCD) technology and HV (high voltage) CMOS technology. As a result, many electrical control units (ECUs) previously installed in automotive systems are now replaced with chips fabricated by HV processes to replace abundant discrete components. These ECUs cover telematics communication, in-vehicle networking, and X-by-wire control systems (X = steer, break, accelerate, A/V, safety, etc.). For the sake of safety, these transceivers in ECU are particularly required with high voltage tolerance and high current protection, e.g., a FlexRay transceiver must possess  $\pm 60$  V tolerance and 90 mA of maximum peak current when bus is short-circuited in 60 V within 400 ms [3].

Recently, many research or products regarding the FlexRay transceivers have been published [4]–[10]. For example, FlexRay transceivers fabricated using a typical 0.18  $\mu$ m CMOS

Manuscript received February 16, 2014; revised May 16, 2014, June 28, 2014, and September 25, 2014; accepted November 09, 2014. Date of publication December 08, 2014; date of current version February 23, 2015. This paper was recommended by Associate Editor A. Mazzanti.

C.-C. Wang, C.-L. Chen, Z.-Y. Hou, and Y. Hu are with Department of Electrical Engineering, National Sun Yat-Sen University, Kaohsiung 80424, Taiwan (e-mail: ccwang@ee.nsysu.edu.tw).

J.-W. Lee, W.-Y. Lin, Y.-F. Chang, C.-W. Hsu, and M.-H. Song are with Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu 300-78, Taiwan (e-mail: jwleea@tsmc.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2014.2370192

process were proposed to justify their functionalities in low voltage domain [4]–[6]. According to FlexRay specification [3], they will not pass high voltage specifications, e.g.,  $\pm 60$ V tolerance and  $-10 \sim +15$  V common mode input voltage of the receiver (Rx). Although a FlexRay communication network with Active Star was physically implemented using ALTERA Excalibur ARM EPXA4F672C3 [7], it only verified the functionality, not the reliability and safety required by the physical FlexRay systems. Another FlexRay transceiver was implemented using a 0.35  $\mu m$  CMOS high voltage technology [8], [9]. This design neither resolved the  $\pm 60$  V fault tolerance problem, nor did it address the high voltage ESD requirement. Another famous FlexRay transceiver was fabricated by SOI technology [10]. Referring to technical considerations for automotives [11], the SOI technology is not well suited for power devices, e.g., automotive chip, since the thermal conductivity of oxide is very low. In addition, the SOI technology is quite expensive and the integration is not very easy and straightforward, e.g., vertical components and ESD protection cells. By contrast, BCD technology with high power capabilities (BiMOS technology) and integration feasibility between analog and digital devices (CMOS technology) is considered a better alternative. Besides, BCD technology also has better area efficiency [12], where low voltage devices are widely used as much as possible and many external components are able to be implemented on silicon.

Another serious challenge in automotive systems is ESD protection, since multiple supply voltage systems are often needed [13]. Particularly, FlexRay transceivers must be tolerant of high voltage and temperature, i.e.,  $-40 \,^{\circ}\text{C} \, \sim \, +125 \,^{\circ}\text{C}$ , besides the voltage requirements that mentioned above. Referring to [14], BCD technology provides excellent ESD protection because of the multiple layers. Moreover, several ESD protection designs are used in BCD technology which have been reported [14]–[16]. These prior works, however, could not apply to  $\pm 60$  V and bi-directional applications such that they are inappropriate for FlexRay transceivers.

Many advanced semiconductor processes have been provided to fabricate HV devices on silicon lately, e.g., 0.25  $\mu$ m 1-poly 3-metal HV BCD process [17]. This particular process offers digital cell library, low voltage MOSs driven by 5 V, and several types of high voltage MOS devices. The most critical limitation is that the gate to source voltage of high-voltage MOS transistors must be limited under a low voltage  $\approx$ 5 V. Therefore, those prior works are not easy to be directly implemented and used this HV BCD process. In this work, we propose a new FlexRay transceiver and a base-floating PNP in ESD protection to resolve all the problems we mentioned. In Section II, the proposed FlexRay transceiver is disclosed, where transmitter (Tx)

1549-8328 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

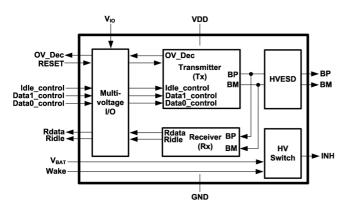

Fig. 1. Explosive view of the proposed FlexRay transceiver (FRT).

TABLE I THE BASIC FUNCTIONS OF FLEXRAY TRANSCEIVER

| State         | S0 | S1 | S2           | S3              |

|---------------|----|----|--------------|-----------------|

| Wake          | 0  | 0  | 1            | 1               |

| RESET         | 1  | 0  | 0            | 0               |

| Idle_control  | 0  | 1  | 0            | 0               |

| Data1_control | 0  | 0  | 0            | $1 \setminus 0$ |

| Data0_control | 0  | 0  | 0            | $0\backslash 1$ |

| BP/BM         | 0  | 0  | Idle (2.5 V) | 1\0             |

| Rdata         | 0  | 0  | 0            | 1\0             |

| Ridle         | 0  | 1  | 1            | 0               |

| INH           | 0  | 0  | $V_{BAT}$    | $V_{BAT}$       |

S0: RESET is activated to reset the FlexRay transceiver

S1: FlexRay transceiver is in the sleep mode.

S2: FlexRay transceiver is in the standby mode.

S3: FlexRay transceiver is in the normal mode.

and receiver (Rx) are included. Particularly, an over-voltage detector is in charge of detecting the abnormal voltage status on bus (BP and BM). Notably, the proposed high-voltage diode can eliminate the negative leakage current. In Section III, the structure of the base-floating PNP is shown and analyzed, which is a bi-directional component. The device can protect the FlexRay transceiver whenever it is exposed to short-circuited hazards at the presence of a positive or negative high voltage. In Section IV, we demonstrate the measurement results of the proposed FlexRay Tx/Rx. The performance comparison between our proposed design and prior works is also discussed. Finally, a brief conclusion is given in Section V.

# II. ARCHITECTURE OF 60 V TOLERANT FLEXRAY TRANSCEIVER

Fig. 1 shows the proposed FlexRay transceiver (FRT) in this work, including Multi-voltage I/O, HV switch, Transmitter (Tx), Receiver (Rx), and high-voltage ESD (HVESD). There are four states describing the functionality of the FlexRay transceiver, as shown in Table I, where Idle\_control, Data1\_control, and Data0\_control are used to drive the Tx for transmitting data on bus (BP and BM). The Wake signal will turn on the HV Switch to drive off-chip power devices, including DC/DC converters. Multi-voltage I/O is in charge of converting these input signals into the voltage range between VDD and GND by adjusting V<sub>IO</sub>. Notably, the Rx monitors the bus status to distinguish whether the data arrive or not. Most important of all, these high-voltage devices are protected by HVESD against electrostatic hazards. The functions of each block are described as follows:

## A. Transmitter (Tx)

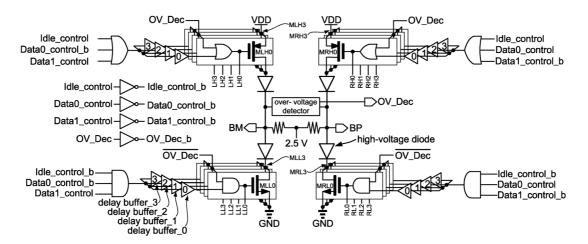

A delay-based transceiver with an over-voltage detector utilizing a LVDS-like transmitter design [18], [19] is proposed in this work, as shown in Fig. 2. When Idle\_control is activated, BP and BM are locked on 0 V. Otherwise, BP and BM are pulled up to 2.5 V. Data0\_control and Data1\_control drive the high-voltage MOSs, i.e., MLH0~MLH3, MLL0~MLL3, MRH0~MRH3, and MRL0~MRL3. For instance, if Data0\_control is 1 and Data1\_control is 0, BP is pulled down and BM is pulled high such that a logic "0" is transmitted over the bus.

Notably, the transitions of high-voltage PMOS transistors and NMOS transistors could not be synchronized perfectly in prior works [18]. A large current will be generated on bus (BP and BM), if they are accidently turned on at the same time, namely "glitch." These delay buffers, i.e., delay buffer\_0~delay buffer\_3, are added to resolve this problem. Besides, the high-voltage PMOS and NMOS transistors are equally divided into many transistors, e.g., MLH0~MLH3. Because the size of each transistor is relatively small and the transition time of gate drive thereof also is equally delayed, no large current will be introduced on bus. Therefore, the glitch will be apparently eliminated by properly delaying the transition time of each high-voltage MOS. The functions of the over-voltage detector and high-voltage diodes are described as follows:

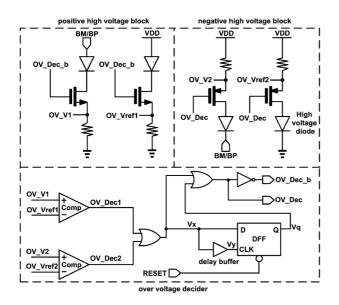

1) Over-Voltage Detector: According to FlexRay specifications, BP and BM are required with high voltage tolerance, i.e., maximum  $\pm 60$  V. Therefore, the over-voltage detector is needed to distinguish whether BP or BM is normally operating. If the voltage of BP/BM is higher than VDD or lower than GND, the over-voltage detector is activated to turn off all high voltage MOSs. The over-voltage detector consists of a positive high voltage block, a negative high voltage block, and an over-voltage decider, as shown in Fig. 3. In the positive high voltage block, there are two symmetrical strings generating OV\_V1 and OV\_Vref1, respectively, where the only difference of these strings is the supply voltage. When the voltage of BM/BP is higher than VDD, OV V1 will be larger than OV Verf1. By contrast, When the voltage of BM/BP is lower than GND in negative high voltage part, OV\_V2 will be smaller than OV Verf2. Therefore, the over voltage decider compares these reference voltages to distinguish whether BP or BM is kept safely within VDD and GND.

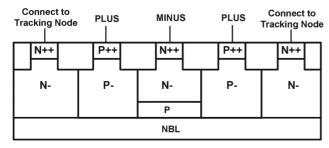

2) High-Voltage Diode: The high-voltage diode is used to block any high voltage and reverse leakage current. For example, when BP or BM is short-circuited in a positive high voltage, the upper high-voltage diodes are used to block any high voltage, and then the bottom high-voltage diodes and MOSs are turned off by the over-voltage detector. By contrast, when BP or BM is short-circuited to a negative high voltage, a large leakage current will be introduced if the traditional diodes are used. The reason is that the traditional diode is implemented by P-N junction such that it is still turned on because the P node is coupled to the negative voltage. Therefore, the high-voltage diode is required to eliminate the leakage current by implanting the NBL layer as the isolation ring, as shown in Fig. 4, where the cross-section view of this diode is disclosed. It is mainly composed of an N- well surrounded with P- well implant layers to prevent the leakage current flowing into the substrate.

Fig. 2. Proposed transmitter (Tx) schematic.

Fig. 3. Over-voltage detector schematic.

Fig. 4. Cross-section view of high-voltage diode.

Moreover, the NBL layer is internally connected to a tracking system, guaranteeing that the voltage of this well always is higher than that of the BP/PM and the substrate. With these two added layers, the diode can sustain high input voltages while maintaining a low leakage current.

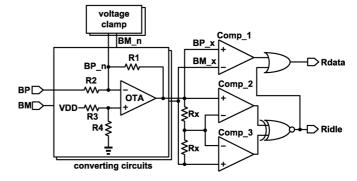

#### B. Receiver (Rx)

FlexRay specifications require that the input common voltage of Rx is  $-10 \sim +15$  V. Therefore, Rx has to convert the BP and BM into the input range of the following comparators, i.e., Comp\_1~Comp\_3, as shown in Fig. 5. The converting circuits consist of OTA, R1~R4, and a voltage clamp, generating BP x

Fig. 5. Proposed receiver (Rx) schematic.

and BM\_x voltage references. BP\_x is constrained by the following equation:

$$BP_x = VDD \times \frac{R4}{R3 + R4} \times \left(1 + \frac{R1}{R2}\right) - BP \times \frac{R1}{R2} \quad (1)$$

where the first term at the right hand side is adjusted as a common voltage. The conversion function is based upon the linear mapping from  $-10 \sim +15$  V to  $0\sim 5$  V such that the ratios of R1/R2 and R3/R4 can be easily calculated. Similarly, BM\_x can also be generated by the converting circuits. Therefore, the three comparators (Comp\_1~Comp\_3) are able to easily recognize the data status on bus, where the comparators are based on a three-stage comparator circuit [20]. Comp\_1 is used to determine if the received data is low or high on bus. Comp\_2 and Comp\_3 are in charge of distinguishing whether any data are transmitted on bus.

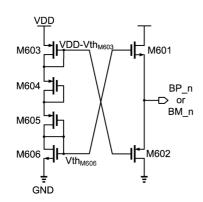

To protect the receiver against high voltage hazards in Fig. 5, the voltage clamp is used to clamp the voltage of BP\_n and BM\_n. Referring to Fig. 6, the left MOS string is used to generate reference voltages, which are "VDD – Vth<sub>M603</sub>" and "Vth<sub>M606</sub>," respectively. Therefore, M601 and M602 must be turned off when BP\_n is within "VDD – Vth<sub>M603</sub> + Vth<sub>M602</sub>" and "Vth<sub>M606</sub> – Vth<sub>M601</sub>." Assume all MOS transistors have same threshold voltage, M601 and M602 must be turned off when BP\_n is within VDD and GND. For example, when BP is short-circuited in a positive high voltage, the voltage of BP\_n is also raised over VDD such that M602 of voltage clamp is turned on to pull down the voltage of BP\_n. By contrast, when BP is short-circuited in a negative high voltage, BP\_n also can be clamped. Therefore, high voltages at BM or BP will be clamped

Fig. 6. Voltage clamp schematic.

Fig. 7. The HV Switch schematic.

Fig. 8. Cross-section view of high-voltage ESD (HVESD).

such that the terminals of the OTAs and comparators won't be threatened.

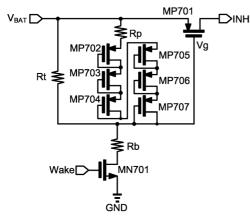

## C. HV Switch

The HW Switch in Fig. 1 is composed of three resistors (Rt, Rb, and Rp), MN701, and MP701~MP707, as shown in Fig. 7, where MN701 and MP701 are HV devices. Notably, Vgs of the HV devices must be smaller than 5 V. The Vgs of MN701 is driven by Wake signal, which is a digital signal with a swing from 0 to 5 V. Therefore, MN701 is ensured safely without any over-voltage hazard. To prevent the over-voltage damage of MP701, the voltage difference between V<sub>BAT</sub> and Vg must be smaller than 5 V. Because Vg is generated by V<sub>BAT</sub>, we separate the voltage range of V<sub>BAT</sub> into two scenarios, i.e., low voltage mode (V<sub>BAT</sub>  $\leq$  5 V) and high voltage mode (V<sub>BAT</sub> > 5 V).

In the high voltage mode, Vg is clamped by Rp and MP702~MP707. In other words, Vg is constrained by the following equation:

$$Vg = V_{BAT} - (V_{Rp} + V_{thpMP702} + V_{thpMP703} + V_{thpMP704} + V_{thpMP705} + V_{thpMP706} + V_{thpMP707})$$

(2)

Fig. 9. Die photo of the proposed FlexRay transceiver.

where  $V_{Rp}$  is the voltage drop of Rp and  $V_{thpMP702} \sim V_{thpMP707}$  are the threshold voltage of MN702 $\sim$ MN707, respectively.  $Vgs_{MP701}$  (Vgs of MP701) is then written as

$$Vgs_{MP701} = V_{Rp} + V_{thpMP702} + V_{thpMP703} + V_{thpMP704} + V_{thpMP705} + V_{thpMP706} + V_{thpMP707} < 5 V$$

(3)

where  $V_{Rp}$  is negligible because Rp is used to limit the peak current of  $V_{BAT}$  such that the MP702 $\sim$ MP707 are prevented from large current hazards.

In the low voltage mode, Vg is generated by Rt and Rb. Therefore, Vg is derived as follows:

$$Vg = V_{BAT} \times \frac{Rb}{Rt + Rb}$$

(4)

Assume Rt is equal to Rb, and Vg is the half of  $V_{BAT}$ . Thus, Vgs of MP701 is half of  $V_{BAT}$  ( $\leq 2.5$  V). Therefore, MP701 is also ensured safely without any over-voltage hazard. Besides, Rt and Rb can be determined based on the requirement of power dissipation. For instance, large Rt and Rb shall reduce dc current to save power.

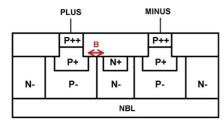

## III. HIGH-VOLTAGE ESD (HVESD)

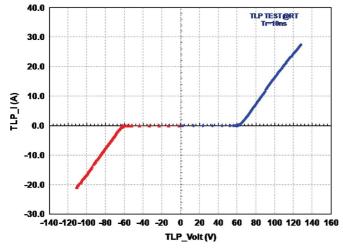

FlexRay specifications demand that bus (BP and BM) pins must pass high level ESD as well as to sustain low leakage current for both high positive and negative voltages, e.g.,  $\pm 60$  V. Traditional ESD devices are usually designed to use in a single direction, e.g., power clamp and I/O ESD cell [14]–[16]. In this work, a high-voltage and bi-directional ESD device is proposed to protect BP and BM pins. As shown in Fig. 8, this ESD device is composed of P- and N- wells. P+ and N+ wells are added to adjust the breakdown voltage. N- well is floating for the bi-directional design. Both PLUS and MINUS nodes provide discharging paths for the ESD current. With a moderate B value in Fig. 8, the proposed ESD device can sustain 60 V breakdown voltage. Besides, this base-floating PNP structure has high holding characteristic and low on-resistance, providing circuit designers a better design window.

## IV. IMPLEMENTATION AND MEASUREMENT

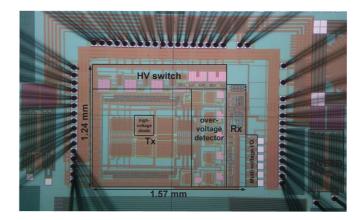

The proposed design is implemented using a  $0.18 \,\mu m$  CMOS mixed-signal based generation II HV BCD process to justify the functionality as well as the reliability. Fig. 9 shows the die photo of the proposed FlexRay transceiver on silicon. The core area is

Fig. 10. Measurement settings of the proposed system.

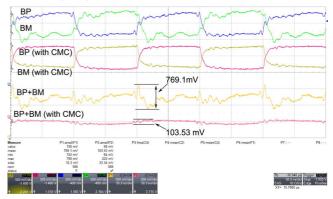

Fig. 11. Measurement waveforms of Tx.

Fig. 12. Measurement waveforms of Rx.

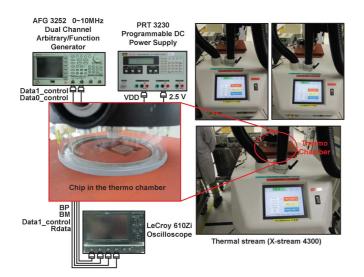

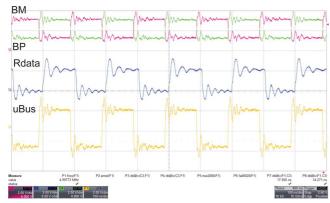

$1.57 \times 1.24 \text{ mm}^2$ . Fig. 10 shows the measurement settings for thermo test between  $-40 \text{ °C} \sim +125 \text{ °C}$ . Fig. 11 shows the physical on-silicon measurement waveforms of the proposed Tx, where Data1\_control and Data0\_control are a pair of digital differential signals. The measurement results show a very good symmetry behavior on BP and BM, where uBus is the difference between BP and BM. The measurement results of Rx are shown in Fig. 12. The comparison between our design and FlexRay specification in different temperature is listed in Table II. All functions are confirmed to FlexRay specifications.

Referring to [21], the output signals of a push-pull type transmitter, e.g., the proposed Tx, will likely become asymmetrical after physical implementation such that a common mode

TABLE II

MEASUREMENT RESULTS OF THE TX/RX IN DIFFERENT TEMPERATURE

| FlexRay Tx Specification              | <b>-40</b> °C | 25° C     | +125°C    |

|---------------------------------------|---------------|-----------|-----------|

| Absolute value of uBus, while sending | 1517 mV       | 1282 mV   | 1081 mV   |

| Transmitter delay, negative edge      | 15.014 ns     | 17.227 ns | 20.047 ns |

| Transmitter delay, positive edge      | 18.634 ns     | 20.309 ns | 23.957 ns |

| Transmitter delay mismatch            | 3.62 ns       | 3.082 ns  | 3.91 ns   |

| Fall time of uBus                     | 10.032 ns     | 12.273 ns | 13.933 ns |

| Rise time of uBus                     | 12.713 ns     | 13.581 ns | 16.826 ns |

| Transition time mismatch              | 2.618 ns      | 1.308 ns  | 2.893 ns  |

| Receiver delay, negative edge         | 16.788 ns     | 17.5 ns   | 24.302 ns |

| Receiver delay, positive edge         | 14.172 ns     | 14.271 ns | 21.835 ns |

| Receiver delay mismatch               | 2.616 ns      | 3.229 ns  | 2.467 ns  |

Fig. 13. Measurement setting of our FRT and NXP TJA1080 with common mode chokes (CMC).

Fig. 14. Measurement results of our FRT with and without CMC.

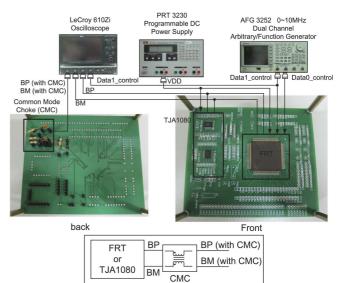

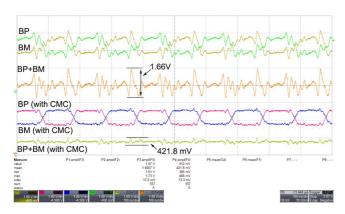

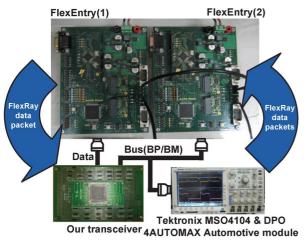

voltage noise is generated. To justify the emission and immunity of the proposed design, a common mode choke (CMC) is used to filter the common mode voltage noise. According to the FlexRay specification [22], the resistance and inductance of CMC are < 1.5  $\Omega$  and 100  $\mu$ H, respectively. Therefore, a commercially available CMC for FlexRay-based systems is used to verify the electromagnetic compatibility (EMC) for differential transmission, namely ACT45R-101-2P [23]. The measurement setting of our FRT and NXP TJA1080 with CMC is shown in Fig. 13. Notably, NXP TJA1080 has been renown as one of the most popular FlexRay transceivers nowadays so that it is used as a golden sample here. Fig. 14 shows the measurement results of FRT with and without CMC, where BP and BM are outputs of FRT without CMC, and BP (with CMC)

Fig. 15. Measurement results of NXP TJA1080 with and without CMC

Fig. 16. Measurement setting with a FlexRay FlexEntry development board.

Fig. 17. Measurement results with a FlexRay FlexEntry development board and DPO 4AUTOMAX automotive module.

and BM (with CMC) are outputs of FRT with CMC. Obviously, the amplitude of common mode voltage noise is reduced from 384.55 mV (0.7691/2 V) to 51.765 mV (0.10353/2 V). To make a fair comparison, the common mode voltage noise of NXP TJA1080 is also measured, as shown in Fig. 15. According to the measurement results, the common mode voltage noise of our proposed FRT is lower than NXP TJA1080, namely 51.765 mV vs. 210.9 mV (0.4218/2 V).

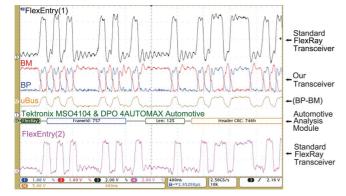

A FlexRay FlexEntry development board is used in the experiment to set up a FlexRay system test environment, as shown in Fig. 16. The FlexEntry(1) generates standard FlexRay packet frames to the proposed transceiver, and then Tx in our transceiver transmits the received data packets to FlexEntry(2) via Bus. The oscilloscope shows the BP and BM signals decoded

Fig. 18. Measurement results of the HV Switch given different  $V_{\rm BAT}$  and 9.1  $K\Omega$  load resistors (RL).

Fig. 19. Measurement results of the over-voltage detector given positive high voltage on BP and BM.

Fig. 20. Measurement results of the over-voltage detector given negative high voltage on BP and BM.

by DPO 4AUTOMAX Automotive module and FlexEntry(2). As expected, all measurement results are matched, as shown in Fig. 17.

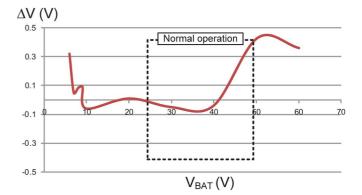

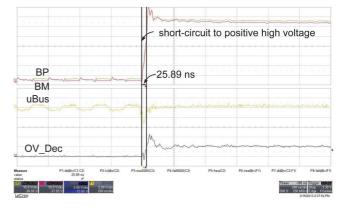

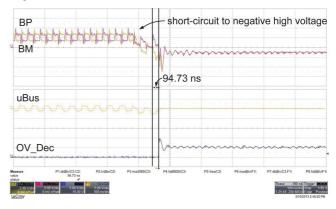

Fig. 18 shows the error distribution with different  $V_{BAT}$  and 9.1 K $\Omega$  load resistors (RL) present at INH in Fig. 1. In the normal operation range ( $24 \text{ V} \leq V_{BAT} \leq 48 \text{ V}$ ), the worst-case voltage between  $V_{BAT}$  and INH ( $\Delta V$ ) is smaller than 0.5 V at > 200  $\mu$ A current load. According to FlexRay specifications, the  $\Delta V$  must be less than 1 V at 200  $\mu$ A current load. Therefore, our proposed HV Switch is confirmed to such a FlexRay specification. Regarding the reliability and safety, the over-voltage detector is tested, as shown in Fig. 19 and Fig. 20, respectively. Referring to Fig. 19, when BP or BM is short-circuited in a positive high voltage, the OV\_Dec is activated to turn off Tx after 25.89 ns. By contrast, Fig. 20 shows the scenario that BP and

TABLE III

COMPARISON OF THE PROPOSED DESIGN AND PRIOR WORKS

| FlexRay Tx/Rx Specification           | This work               | [5]            | [4]             | [24]       | [10]               | FlexRay Specification  |

|---------------------------------------|-------------------------|----------------|-----------------|------------|--------------------|------------------------|

| Year                                  | 2014                    | 2012           | 2010            | 2010       | 2007               | 2010                   |

| Absolute value of uBus, while sending | 1282 mV                 | 950 mV         | 1380 mV         | 4000 mV    | 1600 mV            | 600~2000 mV            |

| Absolute value of uBus, while Idle    | $\approx 17 \text{ mV}$ | $pprox 0 \ mV$ | $\approx$ 30 mV | 30 mV      | 25 mV              | $0 \sim 30 \text{ mV}$ |

| Transmitter delay, negative edge      | 17.227 ns               | 14.8 ns        | 13.32 ns        | 50 ns      | 31 ns              | < 75 ns                |

| Transmitter delay, positive edge      | 20.309 ns               | 16.4 ns        | 13.29 ns        | 50 ns      | 32 ns              | < 75 ns                |

| Transmitter delay mismatch            | 3.62 ns                 | 1.6 ns         | 0.029 ns        | 4 ns       | 1 ns               | <4 ns                  |

| Receiver delay, negative edge         | 16.788 ns               | 36.8 ns        | 9.492 ns        | 80 ns      | 28 ns              | < 75 ns                |

| Receiver delay, positive edge         | 14.172 ns               | 37.2 ns        | 9.065 ns        | 80 ns      | 30 ns              | < 75 ns                |

| Receiver delay mismatch               | 2.616 ns                | 0.4 ns         | 0.427 ns        | 5 ns       | 2 ns               | < 5 ns                 |

| Supply voltage                        | 5 V                     | 3.3 V          | 3.3 V           | 7 V        | 5.5 V              | 5 V                    |

| ESD (HBM)                             | 8 kV                    | N/A            | N/A             | 6 kV       | 8 kV               | 6 kV                   |

| High voltage tolerance on BP/BM       | $\pm 60 \text{ V}$      | 3.3 V          | 3.3 V           | $\pm 40 V$ | $\pm 60 \text{ V}$ | $\pm 60 \text{ V}$     |

| Power dissipation                     | 181.5 mW                | 76.62 mW       | 43.01 mW        | 315 mW     | 192.5 mW           | N/A                    |

Fig. 21. Infrared images of the proposed design before short-circuiting and after short-circuiting.

Fig. 22. Measurement results of high-voltage ESD (HVESD).

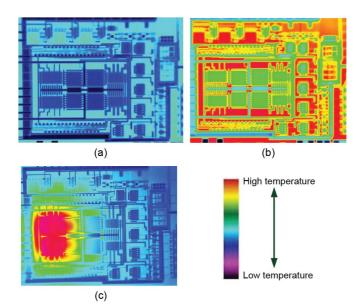

BM are short-circuited in a negative high voltage, where the activating time is less than 94.73 ns. In order to prove the effect of the over-voltage detector, the infrared images demonstrate the relative temperature distribution before and after BP/BM are short-circuited in high voltages, as shown in Fig. 21, where the measurement settings are described as follows:

Fig. 21(a): Over-voltage detector is activated before shortcircuiting.

- Fig. 21(b): Over-voltage detector is activated after when BP and BM are short-circuited in high voltages.

- Fig. 21(c): Over-voltage detector is turned off when BP and BM are short-circuited in high voltages.

Because the over-voltage detector turns off Tx after short-circuiting, the temperature of our proposed design is lower than that of the p-substrate, as shown in Fig. 21(b). By contrast, when the over-voltage detector is turned off, a large leakage current will be generated in Tx after short-circuiting, as shown in Fig. 21(c). Notably, in the scenarios of Fig. 21(c), high voltages on BP and BM cause a huge current to flow back into VDD or GND through these high-voltage MOSs. If the time of such an attack is long, the HV devices will break down.

Fig. 22 shows measurement TLP IV curve of the standalone ESD device. Positive and negative voltage are above  $\pm 60$  V, which are qualified for FlexRay applications. It has reached up to 20 A and HBM test passes 8 kV.

Table III shows the comparison of this work and several prior works. Because the common voltage of Tx is set to 2.5 V in our work, the power consumption is larger than that of the prior works. By contrast, the FlexRay transceivers in [4] and [5] did not have high-voltage tolerance design and high-voltage ESD, which is why their power dissipation is smaller. Referring to Table III, the proposed design attains the lowest power dissipation in those solutions compliant with the FlexRay specifications, including functionality and reliability requirements.

## V. CONCLUSION

In this work, the proposed FlexRay transceiver is equipped with high-voltage tolerance design and high-voltage ESD, which perform the protections of all the required faults in the FlexRay specification. Notably, the proposed design is implemented using a 0.18  $\mu$ m CMOS mixed-signal based generation II HV BCD process such that it is easily integrated with digital circuits. Besides, these protective devices, i.e., high-voltage ESD, high-voltage diode, and the over-voltage detector, are fabricated on the same die and measured to justify their performance. Most important of all, they are able to protect the transceiver from any fault condition of high voltage.

#### ACKNOWLEDGMENT

This investigation is supported by Taiwan Semiconductor Manufacturing Company (TSMC), Taiwan, for their thoughtful chip fabrication service. The authors also like to thank Aim for Top University Plan project of NSYSU and MOE, Taiwan, for partially supporting this investigation. The authors would also like to thank Dr. C.-F. Wu and Mr. W.-F. Tsai of NXP Semiconductors (Taiwan) Ltd. and CIC (Chip Implementation Center) of NARL (Nation Applied Research Laboratories), Taiwan, for their strong support of the thermo chamber equipment and infrared image measurements.

#### REFERENCES

- L. V. Voorde, K. Appeltans, and J. Alonso, "An EMC-robust high voltage system-on-chip," in *Proc. Eur. Solid-State Circuits Conf.*, Sep. 2004, pp. 447–450.

- [2] S. Kaeriyama, S. Uchida, M. Furumiya, M. Okada, T. Maeda, and M. Mizuno, "A 2.5 kV isolation 35 kV/µs CMR 250 Mbps digital isolator in standard CMOS with small transformer driving technique," *IEEE J. Solid-State Circuits*, vol. 47, no. 2, pp. 435–443, Feb. 2012.

- [3] FlexRay Communication System Electrical Physical Layer Specification V3.0.1 [Online]. Available: http://www.flexray.com 2010

- [4] C.-C. Wang, G.-N. Sung, P.-C. Chen, and C.-L. Wey, "A transceiver frontend for electronic control units in FlexRay-based automotive communication systems," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 2, pp. 460–470, Jan. 2010.

- [5] C.-C. Wang, C.-L. Chen, J.-J. Li, G.-N. Sung, T.-H. Yeh, and C.-Y. Juan, "A low-power transceiver design for FlexRay-based communication systems," *Microelectron. J.*, vol. 44, no. 4, pp. 359–366, Apr. 2013.

- [6] S.-H. Zheng, Z.-M. Lin, and D.-C. Liaw, "Transceiver design for the bus driver of the FlexRay communication system," in *Proc. Soc. In*strum. Control Eng. Annu. Conf., Aug. 2010, pp. 3625–3630.

- [7] Y.-N. Xu, C.-H. Jeon, and J.-G. Chung, "Design of FlexRay communication network using active star," *Mod. Appl. Sci.*, vol. 4, no. 4, pp. 34–41, Apr. 2010.

- [8] F. Baronti, P. D'Abramo, M. Knaipp, and R. Minixhofer *et al.*, "FlexRay transceiver in a 0.35 μm CMOS high-voltage technology," in *Proc. Design, Autom, Test Eur.*, Mar. 2006, vol. 2, pp. 1–5.

- [9] F. Baronti, E. Petri, S. Saponara, L. Fanucci, and R. Roncella *et al.*, "Design and verification of hardware building blocks for high-speed and fault-tolerant in-vehicle networks," *IEEE Trans. Ind. Electron.*, vol. 58, no. 3, pp. 792–801, Mar. 2011.

- [10] NXP DataSheet: TJA1080, FlexRay Transceiver, Jul. 2007.

- [11] H. Casier, P. Moens, and K. Appeltans, "Technology considerations for automotive," in *Proc. Eur. Solid-State Circuits Conf.*, Sep. 2004, pp. 37–41.

- [12] A. Danchiv, M. Hulub, and D. Manta, "An area efficient multi-channel high side switch implementation," in *Proc. Eur. Solid-State Circuits Conf.*, Sep. 2011, pp. 327–330.

- [13] A. Gendron, C. Gill, C. Zhan, M. Kaneshiro, B. Cowden, C. Hong, R. Ida, and D. Nguyen, "New high voltage ESD protection devices based on bipolar transistors for automotive applications," in *Proc. Electr. Overstress/Electrostatic Discharge Symp.*, Sep. 2011, pp. 1–10.

- [14] R. Zhu, F. Yao, S. Wang, A. Wang, L. Wu, X. Zhang, and B. Chi, "A study of process/device/layout co-design for full-chip ESD protection in BCD technology," in *Proc. IEEE Int. Solid-State Integr. Circuit Technol.*, Oct. 2012, pp. 1–3.

- [15] C.-K. Chen, C.-F. Huang, Y.-F. Chang, J.-W. Lee, S.-M. Cheng, and M.-H. Song, "Schottky emitter high holding voltage ESD clamp in BCD power technology," in *Proc. Electr. Overstress/Electrostatic Discharge Symp.*, Sep. 2012, pp. 1–6.

- [16] W.-Y. Chen and M.-D. Ker, "Circuit and layout co-design for ESD protection in Bipolar-CMOS-DMOS (BCD) high-voltage process," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 5, pp. 1039–1047, May 2010.

- [17] S.-H. Yang, J.-W. Liu, and C.-C. Wang, "A signal-chip 60-V bulk charger for series li-ion batteries with smooth charge-mode transition," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 7, pp. 1588–1597, Jul. 2012.

- [18] C.-L. Chen, Z.-Y. Hou, S.-C. Lin, and C.-C. Wang, "A delay-based transceiver with over-current protection for ECU nodes in automobile FlexRay systems," in *Proc. Int. Conf. Consum. Electron.*, Jan. 2013, pp. 610–611.

- [19] C.-C. Wang, C.-L. Lee, C.-Y. Hsiao, and J.-F. Huang, "Clock recovery and data recovery design for LVDS transceiver used in LCD panels," in *Proc. IEEE Asia Pacific Conf. Circuits Syst.*, Dec. 2004, vol. 2, pp. 861–864.

- [20] R. J. Baker, H. W. Li, and D. E. Boyce, CMOS Circuit Design, Layout, and Simulation. Piscataway, NJ, USA: IEEE Press, 2010.

- [21] D. Paret, FlexRay and Its Applications: Real Time Multiplexed Network. Hoboken, NJ, USA: Wiley, 2012, pp. 138–142.

- [22] FlexRay Electrical Physical Layer Application Notes V3.0.1, 2010.

- [23] TDK DataSheet: ACT45R-101-2P, Common Mode Filters for FlexRay, Nov. 2013.

- [24] Austriamircosystems DataSheet: AS8223, FlexRay Active Star IC, Nov. 2010.

**Chua-Chin Wang** (M'9–SM'14) received the Ph.D. degree in electrical engineering from State University of New York (SUNY) at Stony Brook, NY, USA, in 1992. He then joined the Department of Electrical Engineering, National Sun Yat-Sen University (NSYSU), Taiwan, and became a full Professor in 1998. He was Chairman of Department of Electrical Engineering, NSYSU, during 2009–2012. Dr. Wang's research interests include memory and logic circuit design, communication circuit design, and interfacing I/O circuits. Particularly, he applies

most of his research results on biomedical, memories, consumer electronics, and wireless communication applications, such as implantable ASIC/SOC, DVB-T/H and car electronics circuits, low power memory, high speed digital logic, etc. He was elevated to be Distinguished Professor of National Sun Yat-Sen University in 2010 and ASE Chair Professor in 2013. He became an IET Fellow in 2012. He is Dean of Engineering College, NSYSU, since 2014.

Prof. Wang was Chair of IEEE Circuits and Systems Society (CASS) for 2007~2008, Tainan Chapter. He was also the founding Chair of IEEE Solid-State Circuits Society (SSCS), Tainan Chapter for 2007~2008, and the founding Consultant of IEEE NSYSU Student Branch. He was Chair of IEEE CASS Nano-electronics and Giga-scale Systems (NG) Technical Committee for 2008~2009. Since 2010, he has been invited to be an Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—PART I: REGULAR PAPERS and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—PART II: EXPRESS BRIEFS. Dr. Wang was General Chair of 2007 VLSI/CAD Symposium. He was General Co-Chair of 2010 IEEE International Symposium on Next-generation Electronics (2010 ISNE). He was Conference Chair of 2011 IEEE International Conference on IC Design and Technology (2011 ICICDT), and General Chair of 2012 IEEE Asia-Pacific Conference on Circuits and Systems (2012 APCCAS).

**Chih-Lin Chen** (S'10) was born in Taiwan in 1986. He received B.S. and M.S. degrees in electrical engineering from National Sun Yat-Sen University, Kaohsiung, Taiwan, in 2008 and 2010, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering.

He was a Visiting Scholar with Brandenburgische Technische Universität, Cottbus, Germany. His current research interests include VLSI design, high voltage mixed-signal circuit design, automobile system design, and sigma-delta ADC design.

**Zong-You Hou** was born in Taiwan in 1989. He received the B.S. degree in electronic engineering from National Sun Yat-Sen University, Kaohsiung, Taiwan, in 2012, where he is currently pursuing the M.S. degree in electrical engineering. His recent research interest focuses on analog design.

Yi Hu was born in Taiwan in 1989. He received the B.S. and M.S. degrees in electronic engineering from National Sun Yat-Sen University, Kaohsiung, Taiwan, in 2011 and 2013. His recent research interest focuses on analog design.

Jam-Wem Lee was born in Taitung, Taiwan, on November 10, 1973. He received the B.S. and Ph.D.degrees in electronics engineering from the National Chiao Tung University, Hsinchu, Taiwan, in 1996 and 2002, respectively. During this period, he devoted his efforts on improving the reliability and scalability of nanoscaled thin dielectric films. From 2001 to 2002, he was with the United Microelectronics Corporation, Taiwan, as an Engineer working on the electrostatic discharge (ESD) circuit design. After that, he joined the National Nano

Device Laboratories, Hsinchu, as an Associate Researcher for four years. Since 2007, he has been with the Taiwan Semiconductor Manufacturing Company, Hsinchu, as a Section Manager.

**Wan-Yen Lin** received the B.S. degree from the Department of ElectorPhysics, National Chiao Tung University, Hsinchu, Taiwan, in 2009 and the M.S. degree from the Department of Electrical Engineering, National Chiao Tung University in 2011. After that, she joined Taiwan Semiconductor Manufacturing Company, Taiwan, and she is currently a TCAD engineer in the EOS/ESD department.

Chia-Wei Hsu was born in Taipei, Taiwan in 1986. He received the B.S degree from the Department of Engineering and System Science from National Tsing Hua University, Hsinchu, Taiwan, in 2008 and the M.S. degree from the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, in 2010. In 2010, he joined Taiwan Semiconductor Manufacturing Company Ltd (TSMC). He is presently with the EOS/ESD Technology Programs, TSMC. His researches focus on the development and design of ESD protection

devices for power management application.

and I/O interface circuit.

reliability, on-chip ESD protection, standard cell,

**Yi-Feng Chang** received the B.S. degree from the Department of Physics, National Chung Hsing University, Taiwan, in 2003 and the M.S. degree from the Department of Electrical Engineering, National Chiao Tung University, Taiwan, in 2005. From 2005 to 2010, he was with the Nanya Technology Corporation, Taiwan, as a TCAD Engineer working on device development. After that, he joined the Taiwan Semiconductor Manufacturing Company, Taiwan. His research activity focuses on the ESD robustness prediction of semiconductor device and ESD device development.

opment through physical simulation.