# An Implantable SOC Chip for Micro-stimulating and Neural Signal Recording

Chua-Chin Wang, Senior Member, IEEE, Chi-Chun Huang, Tzung-Je Lee, Cheng-Mu Wu, Gang-Neng Sung, Kuan-Wen Fang, Sheng-Lun Tseng, and Jia-Jin Chen

Department of Electrical Engineering National Sun Yat-Sen University Kaohsiung, Taiwan 80424 email : ccwang@ee.nsysu.edu.tw

Abstract—An implantable SOC chip for micro-stimulation and neural signal recording is presented. This work possesses a multi-parameter control protocol to provide different stimulation waveforms, for various pain treatments of muscles and stimulating applications. Additionally, the proposed SOC chip supports several transmission rates of RS232, which in turn provides a flexibility to be integrated in a variety of different applications. Moreover, an IA (instrument amplifier) with CMRR of 120 dB and the stopband attenuation of 38 dB/dec is employed, which is capable of sensing very low voltage (1 to 10  $\mu$ V) neural signal. The proposed design is implemented using TSMC 2P4M 0.35  $\mu$ m CMOS process.

*Keywords*—implantable, wireless, neural stimulation, neural signal recording

Keywords : implanttable, wireless, neural stimulation, neural signal recording

## I. INTRODUCTION

The implantable micro-stimulators are widely used in the treatment of the bladder leakage control [1], interrupt of pains, shaking syndromes of Parkinson's disease [2], muscle nerve stimulation [3], and cochlear implants [4]. Moreover, the stimulus frequency, current, and waveform of each application are different. We tend to design an SOC to serve such a demand.

The sensing of the neural signals and the recording thereof allow the use of the sensory signals as either feedback information or observational data to control the implanted devices, which can be a part of a neuroprosthesis. Notably, the neural signals possess a low signal amplitude in the range of 1 to 10  $\mu$ V, and low frequency in the spectrum between 100 Hz to 7 KHz. Therefore, an IA, which is in charge of faithfully picking up vague neural signals hidden in the background noise floor, plays a critical role in neural signal recording. Important measurements to justify the IA include CMRR (common-mode reject ratio, > 90 dB), stopband attenuation (> 30 dB/dec), and high gain (> 80 dB). The reason why these measurements are so important is to reject the unwanted noise and to amplify the very weak neural signal.

Furthermore, data and power transfer between the implantable unit and the outside world should be achieved without interconnect wires to avoid the infection at the points where the skin is broken. However, the transmission bit rate has a critical limit resulted from the induction of the outside and inside coils. This may cause data congestion when the neural signal is recorded.

This work presents an implantable SOC chip for wireless neural micro-stimulation and neural signal recording. The proposed chip possesses a multi-parameter communication protocol to generate different stimulus currents for various pain treatments of muscles. Moreover, the baseband circuit can support various transmission data rates of the RS232 interface. Therefore, the proposed chip is flexible for applying to various wireless induction devices and the transmission rate can be decided by the user.

#### II. THE STRUCTURE OF THE IMPLANTABLE SOC

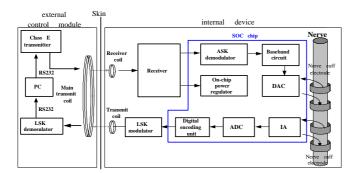

We propose an implantable SOC to carry out the controllable micro-stimulation mission utilizing wireless and non-penetrating transmission to accept external instructions and execute required stimulations. In dual respect, the target SOC chip is also expected to sense the response of the nerves, convert into wireless signals and finally send back to the external monitoring devices. The infrastructure of the entire electrical micro-stimulation system is given in Fig. 1.

# A. Power regulator

Since the power of the core circuits on the chip is generated by the induced RF signal, a power regulator is needed to generate a stable system voltage which possesses a ripple less than 10% variation.

# B. C-less ASK demodulator

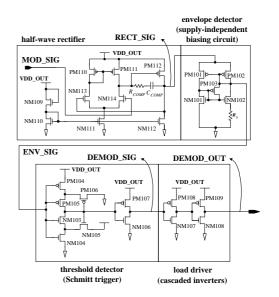

The C-less ASK demodulator is divided into four part: (1) buffered half-wave rectifier, (2) envelope detector, (3) threshold detector, and (4) load driver, as shown in Fig. 2 [5]. Notably, a two-stage OPA (operational amplifier) acts as an unit gain buffer which passes the positive voltage and resists the negative voltage. Thus, it is basically a half-wave rectifier.

#### C. Stimulation DAC

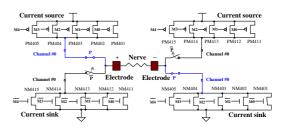

The 5-bit current steering DACs are employed to supply binary-weighted driving currents to their associative nerves to serve as a stimulus. The polarity signal (P) from the decoder is used to control the switches to select the current direction such that the biphase stimulus can be achieved.

# D. Instrumentation amplifier, IA

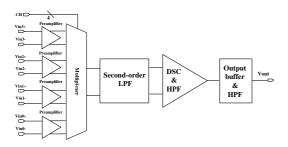

The structure of the proposed 4-stage IA is shown in Fig. 4 [6]. It is composed of four cascaded stages : a preamplifier, a 2ndorder LPF (low-pass filter), a DSC (differential-to-single converter) with HPF (high-pass filter), and an output buffer with HPF. The first stage, which is the preamplifier, is mainly in charge of reducing the thermal noise effect. The 2nd-order LPF is to increase the DC gain and the stopband attenuation by adding a pole around 7 KHz using the modified low-noise gm-C LPF design in [7]. The DSC with HPF stage is to define a pole at 100 Hz and convert the differential signal into a single-ended signal such that the following ADC can further convert the sensory signal into a binary format for digital signal processing. The last stage adds another high-pass pole at 100 Hz such that the stopband attenuation can be enhanced.

# E. ADC

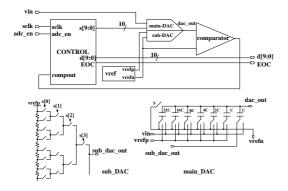

A charge-redistribution successive approximation ADC (SA ADC) is employed in this work, as shown in Fig. 5. A binary search through all possible quantization level is performed to obtain the final digital value. In order to avoid the drastically increased area of the binary-weighted capacitor array due to the higher resolution of SA ADC, a 6-bit binary-weighted capacitor array and a 4-bit resistor string DAC are combined to construct the 10-bit DAC. Additionally, a four-stage comparator is utilized such that the input voltage difference is amplified stage by stage. Thus, the input equivalent capacitor of the comparator can be reduced so that the matching of the binary-weighted capacitor array is ensured.

# F. Packet format

The control command are issued by the external PC. The proposed chip can accept the data packet format which follows the RS232 standard with Baud Rate of 2400, 4800, 7200, 9600, 12800, 14400, 19200, 28800, 38400, 57600, 115200, and 125000 bps (bits per second). The valid packets of the command are listed in Table I. There are a total of 10 bits in each packet. The first bit, "0," is the RS232 start bit and the last bit, "1," is the end bit of RS232. The first two packets are the synchronization packets. The third packet which contains a "0011" string is the start packet. The next three packets are the data packets of the first command, which determines the action by those parameters, explained in Table II. The parameters in the first two data packets trigger the corresponding stimulations, while the third is to execute neural signal recording and impedance measurement.

The packet format provides three operation modes: neural micro-stimulation, neural signal recording, and impedance measurement. When the parameter FUN = 00, the neural stimulation is performed. Several stimulus currents are generated according to the 8 parameters for various muscles neural stimulation applications [8]. Besides, If an extra lower frequence of stimulation needs to be created, the user should choose the "Repeat" function of the GUI. Moreover, the IA and ADC are disabled to reduce the power consumption. When FUN = 01, the neural recording is activated. IA and ADC are enabled such that the neural signal is amplified by IA and digitalized by ADC. Then, the digitalized neural signals are transformed to a serial packet following the RS232 standard, as shown in Table III, for the off-chip LSK modulator. When FUN = 10, the impedance measurement is switched on. DAC generates the required current stimulus and ADC measures the voltage at the same time. Then, the measured data is sent back to PC to be analyzed. Finally, if a control data is received while FUN = 11, the operation mode remains without change.

# G. Baseband circuit

The baseband circuit includes a power-on reset circuit, a 2 MHz clock generator, a clock recovery circuit and a packet decoder. Initially, VDD\_OUT rises from the ground voltage. The built-in clock starts oscillating. Then, the built-in reset signal (the rising edge) resets the digital baseband circuit. When the synchronization packets are received, the clock recovery circuit counts how many cycles of the 2 MHz built-in clock during each positive edge and negative edge of the synchronization packets. The cycle numbers are recorded and then used to generate the system clock. In order to avoid the jitter accumulation of the 2 MHz clock recovery circuit calibrates the system clock every time that the RS232 signal flips its state. Thus, a 0.19  $\mu$ s jitter tolerance is possessed for the 2 MHz clock to recover the system clock correctly.

# III. IMPLEMENTATION AND MEASUREMENT

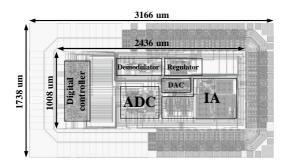

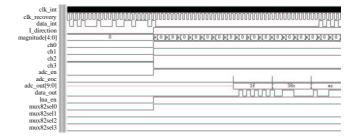

TSMC (Taiwan Semiconductor Manufacturing Company) 0.35  $\mu m$  2P4M CMOS process is adopted to carry out the proposed implantable chip design. The layout of the proposed design is shown in Fig. 6, where the digital controller includes the baseband circuit and the digital encoding unit in Fig. 1. The chip core area is 1008  $\mu$ m × 3166  $\mu$ m (1738  $\mu$ m × 2436  $\mu$ m with pads). Fig. 7 is the snapshot of the GUI on the PC host. Fig. 8 shows the simulation results of continuous mode stimulation and neural signal recording. The system clock is recovered after the synchronous package received. The signal "ch3" is selected to perform the continuous mode stimulation which means that channel 3 continues the stimulus until the next command is received. Additionally, the signal "lna\_en" and "adc\_en" are also activated, and the channel "mux82sel0" is selected to record the neural signal. After ADC converts a sample, the parallel data "adc\_out" is transformed to the serial "data\_out." This process continues until the command which disables the selected recording channel is received. The characteristics of the proposed chip are tabulated in Table IV.

# IV. CONCLUSION

We present an implantable SOC chip for micro-stimulation and neural signal recording system. A multi-parameter control protocol is proposed to provide differential stimulation waveforms for various pain treatments of muscles and stimulating applications. The protocol also can accept different transmission data rates compliant with RS232 standard such that the proposed chip can be easily integrated with PC-based system.

#### ACKNOWLEDGMENT

This research was partially supported by National Science Council under grant NSC 92-2218-E-110-001 and NHRI-EX93-9319EI. The authors would like to thank CIC of National Science Council (NSC), Taiwan, for their thoughtful help in the chip fabrication of the proposed work. The authors also like to thank "Aim for Top University Plan" project of NSYSU and Ministry of Education, Taiwan, for partially supporting the research.

#### REFERENCES

- [1] J. S. Walter, J. S. Wheeler, W. Cai, W. W. King, and R. D. Wurster, "Evaluation of a suture electrode for direct bladder stimulation in a lower motor neuron lesioned animal mode," *IEEE Trans. on Rehabilation Engineering*, vol. 7, no. 2, pp. 159-166, June 1999.

- [2] R. R. Tasker, "Deep brain stimulation is preferable to thalamotomy for tremor suppression," *Surg Neurol.*, vol. 49, no. 2, pp. 145-153, Feb. 1998.

- [3] G. E. Loeb, F. J. R. Richmond, D. Olney, T. Cameron, A. C. Dupont, K. Kood, R. A. Peck, P. R. Troyk, and H. Schulman, "BION<sup>TM</sup> Bionic neurons for functional and therapeutic electrical stimulation," 20th IEEE Engineering in Medicine and Biology Society, vol. 5, pp. 2305-2309, Nov. 1998.

- [4] R. E. Isaacs, D. J. Weber, and A. B. Schwartz, "Work toward real-time control of a cortical neural prosthesis," *IEEE Trans. on Rehabilation Engineering*, vol. 8, no. 2, pp. 196-198, June 2000.

- [5] C.-C. Wang, Y.-H. Hsueh, U Fat Chio, and Y.-T. Hsiao, "A C-less ASK demodulator for implantable neural interface chips," in 2004 IEEE Inter. Symp. on Circuits and Systems, vol. 4, pp. 57-60, May 2004.

- [6] C.-C. Wang, and C.-C. Huang, "A 38-dB stopband attenuation and 120-dB CMRR small-area LNA for neural signal sensing and recording," 2005 Inter. Conf. on Systems and Signals, pp. 137, CD-ROM version, H-III, Apr. 2005.

- [7] A. Uranga, N. Lago, X. Navarro, and N. Barniol, "A low noise CMOS amplifier for ENG signals," 2004 IEEE Inter. Symp. on Circuits and Systems, vol. 4, pp. 21-24, May 2004.

- [8] C.-C. Wang, Y.-H. Hsueh, Y.-T. Hsiao, U Fat Chio, and C.-C. Huang, "An implantable neural interface micro-stimulator chip with external controllability," 2004 The Fourth IEEE Asia-pacific Conf. on Advance System Integrated Circuits (APCCAS 2004) pp. 356-359, Aug 2004.

- [9] R. Rangarajan, J.A. Von Arx, and K. Najafi, "Fully integrated neural stimulation system (FINESS)," 2000 IEEE Midwest Symp. on Circuits and Systems, vol. 3, pp. 1082-1085, Aug. 2000.

- [10] T. Akin, K. Najafi, and R. M. Bradley, "A wireless implantable multichannel digital neural recording system for a micromachined sieve electrode, "*IEEE J. of Solid-State Circuits*, vol. 33, no. 1, pp. 109-118, Jan. 1998.

|         |   | THE CO | MMA | ND P | ACKI | ET FC | ORMA | Т    |     |   |

|---------|---|--------|-----|------|------|-------|------|------|-----|---|

| packet1 | 0 | 1      | 0   | 1    | 0    | 1     | 0    | 1    | 0   | 1 |

| packet2 | 0 | 1      | 0   | 1    | 0    | 1     | 0    | 1    | 0   | 1 |

| packet3 | 0 | 1      | 0   | 1    | 0    | 1     | 0    | 0    | 1   | 1 |

| DATA1_1 | 0 | AD P   |     | Р    | MAG  |       |      |      | 1   |   |

| DATA1_2 | 0 | CONT   | DI  | JR   | 1    | NTV   |      | WAVE | PAR | 1 |

| DATA1_3 | 0 | FUN    |     |      | CH   |       |      | 1    | 0   | 1 |

|         |   |        |     |      |      |       |      |      |     |   |

| END     | 0 | 0      | 0   | 0    | 0    | 0     | 0    | 0    | 0   | 0 |

|         |   |        |     |      |      |       |      |      |     |   |

# TABLE I

# TABLE II

# THE PARAMETERS

| field | description                                                 |

|-------|-------------------------------------------------------------|

| AD    | selecting channel(s) to be enabled                          |

| Р     | determines the polarity of the stimulating current          |

| MAG   | denote the magnitude of the stimulating current             |

| CONT  | the continuous mode selection                               |

| DUR   | the stimulation pulse duration                              |

| INTV  | select the interval time                                    |

| WAVE  | selects the stimulation waveform to be monophase or biphase |

| PAR   | the parity check bit                                        |

| FUN   | function selection                                          |

| CH    | specifying which IA channel to be selected                  |

#### TABLE III THE SENSED DATA PACKET PROTOCOL Sync1 0 0 0 DATA1\_1 0 0 1 FUN ADR B9 B8 1 1

B4

B3 B2

B1

B0 1

DATA1\_2

0 B7 B6

B5

Fig. 1. The building blocks of the implantable system.

TABLE IV COMPARISON WITH PRIOR DESIGNS

|                        | ours               | [9]         | [10]      |

|------------------------|--------------------|-------------|-----------|

| Technology             | CMOS 0.35          | BiCMOS      | BiCMOS    |

|                        | 0.35 µm            |             |           |

| Area(mm <sup>2</sup> ) | 1.738×3.166        | 2×8         | 4×4       |

| IA BW.(Hz)             | 100~7K             | no          | 100~3.1K  |

| IA Gain                | 80 dB              | no          | 100       |

| IA Stopband            | 40 dB/dec          | no          | N/A       |

| attenuation            |                    |             |           |

| IA CMRR                | > 100 dB           | no          | N/A       |

| ADC Resolution         | 10 bits            | no          | 8 bits    |

| Channel                | 4                  | 8           | 2         |

| Stimulus Freq.(Hz)     | 20~10K             | 500~8K      | no        |

| Stimulus Dur.          | 100~2000           | N/A         | no        |

| Power (mW)             | 25.52              | < 25        | 90        |

| Function               | Neural recording,  | Neural      | Neural    |

|                        | Micro-stimulation, | stimulation | signal    |

|                        | Impedance          |             | recording |

|                        | measurement        |             | _         |

Fig. 2. Schematic of the C-less ASK demodulator.

Fig. 3. Schematic of the stimulation DAC.

Fig. 4. Schematic of the IA.

Fig. 5. Structure of the SA ADC.

Fig. 6. Layout of the proposed SOC.

| stocmp roza | 2 Control System Ver | 0.00           |                                                                                    |     |

|-------------|----------------------|----------------|------------------------------------------------------------------------------------|-----|

| Address     | Magnitude            | Dgration       | S AADNMMMM E - S CuuIIIPp E - S FFhhhhF                                            |     |

| C 00        | 00000700             | C 00/100 us    | 0 00000010 1 - 0 00000001 1 - 0 0000001<br>0 00001011 1 - 0 00000001 1 - 0 0000001 |     |

| C 01        | 00001/01             | C 01/ 500 m    | 0 00001011 1 - 0 00000001 1 - 0 0000001<br>0 11001001 1 - 0 00000000 1 - 0 0000000 |     |

|             | 00011/03             |                | Add > 0 11001001 1 - 0 01001101 1 - 0 0000001                                      |     |

| · 10        | 00100/04<br>00101/05 | @ 10/1 ms      | 0 11001001 1 - 0 01001101 1 - 0 0101101                                            |     |

| C 11        | 00110/06             | C 11/2 ms      | < Dekte 0 10000010 1 - 0 01001101 1 - 0 0101101                                    |     |

|             | 01000708             |                | 0 10000010 1 - 0 01010101 1 - 0 0101101                                            | 0 1 |

| Direction   | 01001/09<br>01010/10 | Interval       |                                                                                    |     |

| F 0         | 01011/11             | C 000/0 s      | Delete All                                                                         |     |

|             | 01100/12<br>01101/13 |                |                                                                                    |     |

| 01          | 01110/14             | C 001/100 us   |                                                                                    |     |

|             | 01111/15             | C 010/200 us   |                                                                                    |     |

| Cont        | 10001/17             | C 011/1 ms     |                                                                                    |     |

| © D/No      | 10010/18<br>10011/19 | C 100/3 ms     |                                                                                    |     |

| C 1/Yes     | 10100/20             | @ 101/5 m      | Up Down Reset                                                                      |     |

|             | 10101721             |                |                                                                                    |     |

|             | 40.000               | C 110/10 ms    | Repeat II -                                                                        |     |

| Channel     | Exaction             | C 111/50 me    | Packet data                                                                        | 1   |

| Changel 0   | ○ 00/Disable         |                | Sync_1 : 0 10101010 1 Interval 0 -                                                 | ms  |

| Channel 1   | C 01 / Record        | Phase          | eAuc_s : 0 10101010 1                                                              | 1   |

| Changel 2   | · 10/R-Measure       | C 0/Mono-phase | Sync_3 : 0 10101001 1<br>Data 1 : 0 10000000 1 Sept                                | 1   |

| Channel 3   | C 11/Continue        | · 1/Bi-phase   | Data 2 : 0 01010111 1                                                              |     |

| Chausel 3   | 1 II/Conmine         | (+ 17 Hz-phase | Data 3 ; 0 10011010 1 Quit                                                         | 1   |

Fig. 7. The PC's GUI for generating the command of RS232 standard.

Fig. 8. The simulation results of the baseband circuit.