# A Direct Digital Frequency Synthesizer with CMOS OTP ROM§

Chi-Chun Huang, Guo-Lin Jhuang, and Chua-Chin Wang<sup>†</sup>, Senior Member, IEEE

Department of Electrical Engineering National Sun Yat-Sen University Kaohsiung, Taiwan 80424 email: ccwang@ee.nsysu.edu.tw

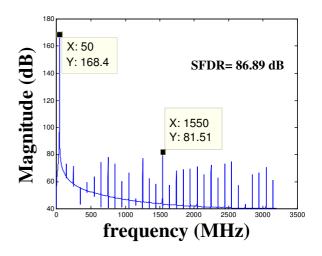

Abstract—A direct digital frequency synthesizer (DDFS) using on-chip CMOS one-time programmable read-only memory (OTP ROM) are presented. A straight-line approximation algorithm for sinusoid with compensation is adopted such that the accuracy could be maintained and the cost is reduced. Most important of all, a CMOS OTP ROM is employed as a look-up ROM table to simplify the ROM fabrication without any additional process steps. The proposed DDFS design is implemented using a typical 1P6M 0.18  $\mu m$  CMOS process. It has a 12-bit amplitude resolution with 86.89 dB spurious free dynamic range (SFDR) using a small ROM size of 256 bits.

Keywords—frequency synthesizer, DDFS, one-time programmable, OTP, straight-line approximation

## I. INTRODUCTION

The frequency synthesizer is an important part of a communication system, particularly in the receiver frontend, where sinusoidal signals are required to shift a high-frequency modulated input signal to an intermediate frequency (IF) band and then demodulate into a baseband signal [1]. The phase-locked loops (PLL) were employed for frequency synthesis traditionally. As the frequency is getting higher, the power consumption becomes a problem in a portable communication device. Compared with PLL, DDFS has faster frequency switching, higher resolution, better spectral purity, lower phase noise, and continuous-phase frequency switching. Moreover, DDFS allows direct phase and frequency modulation in the digital domain [2].

In prior DDFS researches, ROM-based (or namely table look-up) methods have been widely studied, e.g., [7], [8], and [10]. The conventional non-volatile ROM such as EPROM, EEPROM, and flash EEPROM, are manufactured with a special process. As the SOC evolving, the programmable non-volatile memory manufactured with typical logic CMOS process is strongly needed.

Many researches for OTP ROMs have been proposed. Most of them employed either fusing or anti-fusing technology [6], e.g., polyfusing, oxide-nitride-oxide (ONO) [3], metal-oxide-metal (MOM) [4], [5]. Polyfusing is not adaptable with process changing, while the ONO and MOM need

additional process steps. Therefore, none of them is suitable for CMOS-based SOC. With the development of deep-submicron, the gate oxide of transistors becomes very thin which makes the break down very much easy. The transistor can be punched-through (anti-fused) without damaging other circuits. Then, OTP ROM on the CMOS process without any post-process is feasible. This kind of OTP ROM can be used to increase the flexibility and calibratablity of an ASIC or SOC after fabricated. In this paper, we propose a DDFS design using the straight-line approximation for quadrant sinusoid. The error compensation is carried out by a COMS OTP look-up ROM table to save the hardware cost.

## II. THE PROPOSED DDFS DESIGN

# A. Compensated straight line approximation

A perfect sinusoidal wave is cyclic and symmetrical. It could be reconstructed with a quadrant waveform. The straight line approximation is deemed as one of the easiest algorithms to realize with digital circuitry. The classic straight line approximation is to approximate the quadrant sinusoid with n segment straight lines by choosing the closest slope  $m_i$  and intercept  $b_i$ . However, it will increase the cost of operating units to design a high accuracy DDFS in the classic way, if n becomes very large.

The proposed DDFS is divided in two parts, i.e., course approximation block (CAB) and fine approximation block (FAB). The low accuracy approximate waveform will be calculated in CAB part using straight line approximation. By contrast, the error compensation will be carried out by looking up a ROM table to get the waveform with high resolution in FAB part. The sinusoidal wave can be expressed as

$$y(x) = \begin{cases} (m_0 x + b_0) 2^k + e r_0(x), & x_0 \le x < x_1 \\ (m_1 x + b_1) 2^k + e r_1(x), & x_1 \le x < x_n \\ \vdots & & \\ (m_{n-1} x + b_{n-1}) 2^k + e r_{n-1}(x), & x_{n-1} \le x < x_n \end{cases}$$

where x is the output of the phase accumulator, while the  $m_i$ ,  $b_i$  are the slope and intercept of each segment, respectively. The  $er_i(x)$  is the error value of x to compensate the course

<sup>†</sup> the contact author

<sup>§</sup> This research was partially supported by National Science Council under grant NSC 94-2213-E-110-053 and NHRI-EX95-9319EI.

approximation. The k is the shift index for saving the number of multipliers.

## B. DDFS design

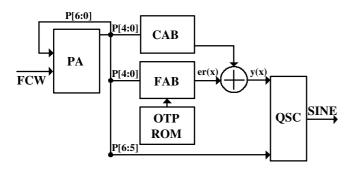

Fig. 1 shows the block diagram of the proposed DDFS design. The phase accumulator (PA) translates the Frequency Control Word (FCW) into control signals of the other function block, P[6:0]. The first two bits of PA output (P[6:5]) are used to reconstruct the complete digital sinusoidal waveform in the quadrant state control (QSC) block. The other bits (P[4:0]) notify the CAB and FAB parts to calculate the quadrant approximate waveform magnitude, y(x). The digital output, SINE, is the complete sinusoidal waveform approximation.

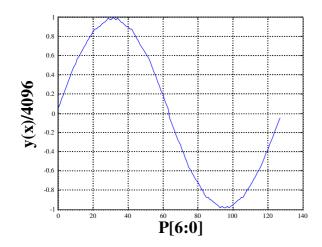

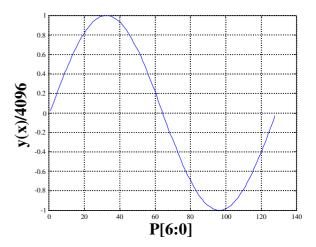

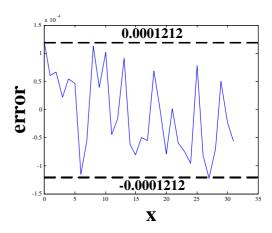

For example, if a DDFS with a 12-bit resolution is needed, k=6 is chosen. Table I is a good combination of coefficients in CAB part after detailed simulations. By Table I, CAB part calculates the course approximation as shown in Fig. 2. Then, we can derive each  $er_i(x)$  by comparing it with the perfect sinusoidal waveform to build the look-up ROM table. The simulation result after error compensation is shown in Fig. 3. Fig. 4 shows the error value between the output waveform and the perfect waveform. Since the largest error value is about  $0.000122 < 2^{12}$ , the amplitude resolution of such a DDFS is 12 bits theoretically.

| i | $m_i$ | $b_i$ | x       |  |  |

|---|-------|-------|---------|--|--|

| 0 | 3     | 3     | 0 ~ 11  |  |  |

| 1 | 2     | 14    | 12 ~ 21 |  |  |

| 2 | 1     | 34    | 22 ~ 29 |  |  |

| 3 | 1     | 32    | 30 ~ 31 |  |  |

TABLE I

THE COEFFICIENT IN MSB PART.

## C. CMOS OTP ROM

Generally, there is a huge equivalent resistance between two sides of gate oxide in a MOSFET fabricated by a standard CMOS process. If high voltage is applied on the gate of the MOSFET, breakdown occurs to reduce the equivalent resistance sharply. This characteristic makes the standard CMOS process possible to realize OTP ROM. As long as we can control the programming time and voltage, we can write the data in the OTP ROM by "anti-fusing" the gate oxide correctly without damaging other circuitry.

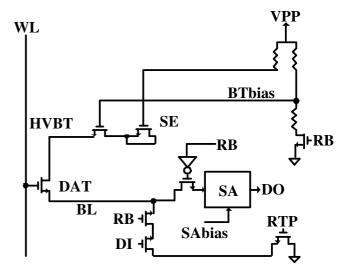

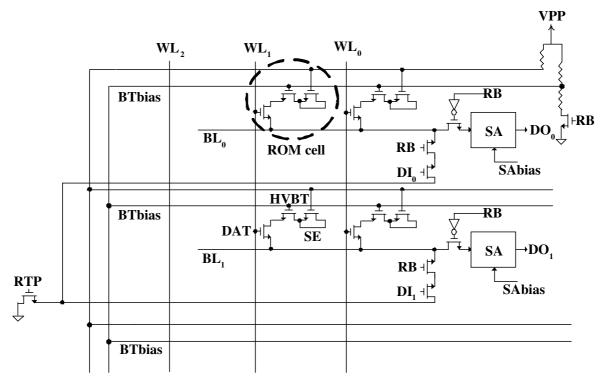

Referring to Fig. 5, the ROM cell is composed of three components: the storage element (SE), the high voltage blocking transistor (HVBT), and the data access transistor (DAT). In the programming mode, the target ROM cell will be selected by enabling word line (WL) and Data\_in (DI). The gate voltage of the SE in the target ROM cell will be pulled high by VPP to anti-fuse the gate oxide. HVBT will be turned on to relay the programming voltage to ground via DAT. The Read\_bar (RB), Data\_in (DI), and Ready\_to\_Program (RTP) will be pulled high to ensure the

current path of target ROM cell in programming mode. In the mean time, HVBT of other ROM cells will be cut off to prevent the programming voltage from damaging their data. In the reading mode. The binary digit stored in SE will be sensed from the current through the DAT, and differentiated by the sense amplifier (SA). In other words, the digit is stored in SE in a resistance state, which can be sensed by a transimpedance amplification. The OTP ROM cell array in the proposed design is shown in Fig. 6.

#### III. IMPLEMENTATION AND SIMULATION

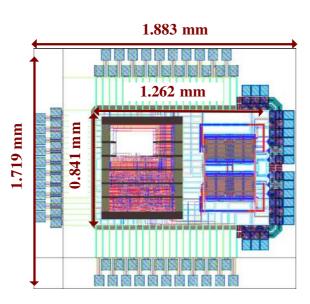

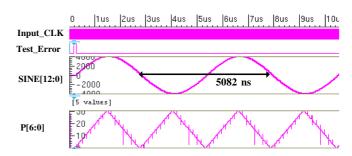

TSMC (Taiwan Semiconductor Manufacturing Company) 0.18  $\mu$ m 1P6M CMOS process is adopted to carry out the proposed chip design. The layout of the proposed design is shown in Fig. 7, The size of the chip core area is 841  $\mu$ m  $\times$  1262  $\mu$ m (1719  $\mu$ m  $\times$  1883  $\mu$ m with pads). Fig. 8 shows the 50 MHz output sinusoidal waveform. Test\_Error is the output of a build-in self test, indicating the correctness of the proposed design. The FFT result of the waveform is shown in Fig. 9, where the spurious free dynamic range (SFDR) is 86.89 dB. The characteristics of the proposed design are tabulated in Table II. The proposed design has the smallest ROM size without sacrificing the amplitude resolution.

|                             | [7]  | [8]  | [9]  | [10] | Proposed Design |

|-----------------------------|------|------|------|------|-----------------|

| process (µm)                | 0.35 | 0.35 | 0.25 | 0.35 | 0.18            |

| amplitude resolution (bits) | 12   | 9    | 12   | 12   | 12              |

| phase resolution (bits)     | 28   | 32   | 24   | 8    | 5               |

| ROM size (bits)             | 448  | 368  | N/A  | 3072 | 256             |

| SFDR (dB)                   | 84.2 | 55   | 80   | 78   | 86.89           |

| MAX. input clock (MHz)      | 320  | 800  | 800  | 300  | 125             |

TABLE II

PERFORMANCE COMPARISON OF DDFSs.

# IV. CONCLUSION

We have proposed a DDFS with a CMOS OTP ROM. The straight line approximation for the quadrant sinusoid has been adopted in addition to the error compensation with small look-up ROM table without any loss of resolution, the proposed DDFS design provides a better solution in terms of ROM size and SFDR.

#### ACKNOWLEDGMENT

The authors would like to thank CIC of National Science Council (NSC), Taiwan, for their thoughtful help in the chip fabrication of the proposed work. The authors also like to thank "Aim for Top University Plan" project of NSYSU and Ministry of Education, Taiwan, for partially supporting the research.

## REFERENCES

- K. I. Palomaki, and J. Niittylahti, "Direct digital frequency synthesizer architecture based on Chebyshev approximation," in Proc. of IEEE Conf. on Signals, Systems and Computers 2000, vol. 2, pp. 1639-1643, Nov. 2000.

- [2] J. Jiang, and E. K. F. Lee, "A low-power segmented nonlinear DAC-based direct digital frequency synthesizer," *IEEE J. of Solid-State Circuits*, vol. 37, no. 10, pp. 1326-1330, Oct. 2004.

- [3] J. Wee, W. Yang, E. Ryou, J. Choi, S. Ahn, J. Chung, and S. Kim, "An antifuse EPROM circuitry scheme for filed-programmable repair in DRAM," *IEEE J. of Solid State Circuits*, vol. 35, no. 10, pp. 1408-1414, Oct. 2000.

- [4] G. Zhang, C. Hu, P. Yu, S. Chiang, S. Eltoukhy, and E. Hamdy, "An electro-thermal model for metal-oxide-metal antifuses," *IEEE Trans. on Electron Devices*, vol. 42, no. 42, pp. 1548-1558, 1995.

- [5] C. Shin, R. Lambertson, F. Hawley, F. Issaq, J. McCollum, E. Hamdy, H. Sakurai, H. Yuasa, Y. Yamaoka, T. Wada, and C. Hu, "Characterization and modeling of a highly reliable metal-to-metal antifuse for high-performance and high-density field-programmable gate arrays," in Proc. of IEEE Int. Symp. on Reliability Physics Symposium, pp. 25-33, Apr. 1997.

- [6] H.-K. Cha, J. Kim, and K. Lee, "A high-density 64k-bit one-time programmable ROM array with 3-transistor cell standard CMOS gateoxide antifuse," *IEEE J. of Semiconductor Technology and Science*, vol. 4, no. 2, pp. 106-109 Jun. 2004.

- [7] J. M. P. Langlois, and D. Al-Khalili, "Novel approach to the design of direct digital frequency synthesizers based on linear interpolation," *IEEE Trans. on Circuits and Systems-II: Analog and Digital Signal Processing*, vol. 50, no. 9, pp. 567-578, Sep. 2003.

- [8] B.-D. Yang, J.-H. Choi, S.-H. Han, L.-S. Kim, and H.-K. Yu, "An 800-MHz low-power direct digital frequency synthesizer with an onchip D/A converter," *IEEE J. of Solid State Circuits*, vol. 39, no. 5, pp. 761-774, May 2004.

- [9] A. G. M. Strollo, D. De Caro, E. Napoli, and N.Petra, "High-speed direct digital frequency synthesizers in 0.25-pm CMOS," in Proc. of IEEE Conf. on Custom Integrated Circuit pp. 163-166, Oct. 2004.

- [10] F. F. Dai, W. Ni, S. Yin, and R. C. Jaeger, "A direct digital frequency synthesizer with fourth-order phase domain noise shaper and 12-bit current-steering DAC," *IEEE J. of Solid State Circuits*, vol. 41, no. 4, pp. 839-850, Apr. 2006.

Fig. 1. The structure of the proposed DDFS.

Fig. 2. The sinusoid approximation without error compensation.

Fig. 3. The sinusoid approximation after compensation.

$Fig.\ 4.\ \ The\ error\ between\ the\ perfect\ waveform\ and\ the\ output\ waveform.$

Fig. 5. The OTP ROM cell.

Fig. 6. The OTP ROM array.

Fig. 7. Layout of the proposed design.

Fig. 8. The simulation of a synthesized sinusoid.

Fig. 9. The SFDR of the synthesized sinusoid.