# A Slew Rate Self-Adjusting 2×VDD Output Buffer With PVT Compensation

Chih-Lin Chen, Hsin-Yuan Tseng, Ron-Chi Kuo, and Chua-Chin Wang<sup>†</sup>, Senior Member, IEEE

Department of Electrical Engineering National Sun Yat-Sen University Kaohsiung, Taiwan 80424 Email: ccwang@ee.nsysu.edu.tw

Abstract—A novel PVT (Process, Voltage, Temperature) detection and compensation technique is proposed to automatically adjust the slew rate of a 2×VDD output buffer. The threshold voltage (Vth) of PMOSs and NMOSs varying with process, voltage, and temperature deviation could be detected, respectively. The proposed design is implemented using a typical 90 nm CMOS process to justify the performance. By adjusting output currents, the slew rate of output signal could be compensated over 38% and the maximum data rate with compensation is 345 MHz.

Index Terms—PVT variation, threshold voltage detection, mixed-voltage tolerant, I/O buffer, floating N-well circuit, gate-oxide reliability

#### I. Introduction

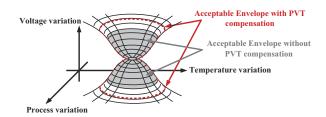

THE sensitivity of modern VLSI circuits to the process, voltage, and temperature (PVT) variation severely degrades performance and yield, especially when the technology is evolved toward nano-scale. The performance of VLSI circuits on silicon can be interpreted as a function of PVT variation, as shown in Fig. 1 [1]. Lately, many prior works have proposed different techniques to enhance the capability against PVT variation and enlarge the acceptable envelop as much as possible to increase the yield. Though the logic delay method has been widely utilized to detect PVT variation [2]-[7], it can only recognize three corners, TT, FF, and SS. Therefore, from a perspective view of transistor level, a novel corner detection technique is needed to detect all process corners, i.e., TT, FF, SS, SF, and FS. That is, the process variation of PMOS and NMOS should be examined, respectively.

In past several years, many mixed-voltage I/O buffers were reported to deal with the chip interface problems of different voltage levels [8]. However, the transmitting and receiving frequency of most previous works are not high enough to meet certain required specification, e.g., PCI-express, which is up to 266 MHz. Therefore, a wide range I/O buffer able to simultaneously transmit and receive signal from VDD to  $2\times VDD$  is deemed as a total solution for these scenarios. To communicate the signal with  $2\times VDD$  swing, double stacked transistors are used in the output stage to avoid the gate-oxide overstress. Moreover, for the high-speed interface circuits, the specification of slew rate is definitely required by communication system protocols. Hence, a compensation mechanism

†: Prof. C.-C. Wang is the contact author.

integrated with the NMOS and PMOS process corner detectors is needed to self-adjust the slew rate of output buffers, as shown in Fig. 2.

Fig. 1. Performance envelop as a function of process and temperature varitaion.

Fig. 2. The slew rate is compensated through our system

## II. 2×VDD OUTPUT BUFFER WITH PVT COMPENSATION

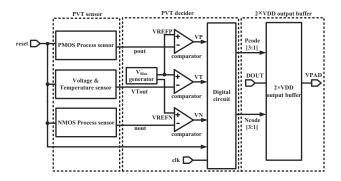

Fig. 3 shows the block diagram of the proposed buffer design for mixed-voltage circuits. The proposed design is composed of PVT sensors, PVT decider, and a  $2\times VDD$  output buffer. The PVT sensors consist of PMOS Process sensor, NMOS Process sensor, and Voltage & Temperature sensor. Notably, the PVT decider comprises three comparators, a  $V_{\rm Bias}$  generator, and a Digital circuit.

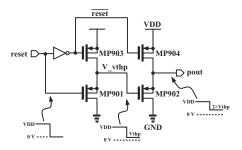

## A. PMOS Process sensor

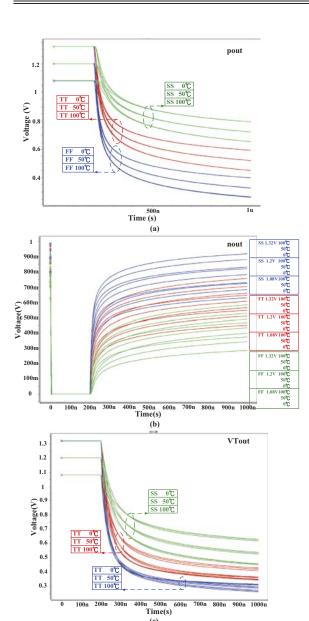

Fig. 4 shows the schematic of a PMOS process sensor. The PMOS process sensor comprises 2 cascaded PMOS source followers, which are composed of MP901  $\sim$  MP904. In the first cycle, if reset is activated, then V\_vthp1 is pulled high to VDD (=1.2 V). In the second cycle, when reset is pulled low, V\_vthp1 is discharged till Vthp, which is the threshold voltage of MP901. By a similarly operation, pout will be discharged

Fig. 3. The block diagram of the proposed output buffer

till 2×Vthp in the second cycle. In other words, the variation of PMOS threshold voltage is "magnified" twice at the output, pout. Finally, the voltage of pout is transmitted to the following PVT decider to detect the PMOS corner.

Fig. 4. Schematic of PMOS process sensor

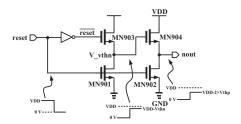

## B. NMOS Process sensor

Fig. 5 shows the schematic of an NMOS process sensor. Similarly, the NMOS process sensor also uses 2 cascaded NMOS source followers, which are composed of MN901 ~ MN904, to detect the NMOS threshold voltage deviation. In the first cycle, when reset is activated, V\_vthn is pulled low to GND (= 0V). In the second cycle, after reset is pulled low, V\_vthn is charged till VDD-Vthn, where Vthn is the threshold voltage of MN904. By a similarly operation, nout will be charged till VDD-2×Vthn in the second cycle. Therefore, the 2 cascaded NMOS source followers generate a VDD-2×Vthn voltage, which is nout, to transmit to PVT decider. Again, the cascaded source follower again "magnify" the NMOS threshold voltage and the variation herewith.

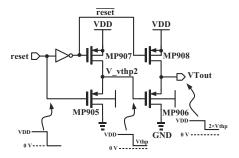

# C. Voltage & Temperature sensor

Fig. 6 shows the schematic of Voltage & Temperature sensor. This sub-circuit employs cascaded source followers to generate 2×Vthp, which is similar to the PMOS Process sensor. The difference is that all bulks are coupled to VDD to generate the body effect in each PMOS. By monitoring the variation of PMOS transistor's Vthp, the voltage and temperature variations can be derived as long as the bulk of the PMOS transistor is coupled to VDD.

Fig. 5. Schematic of NMOS process sensor

1) According to Eqn. (1), the Vthp of MOS with body effect will drift at different Vbs, which is the voltage difference between VDD and source voltage of MOS. Notably, Vthp0 is the no body effect threshold voltage,  $\gamma_p$  is the body effect coefficient, Vfn is the bulk surface potential, Vbs is the voltage difference between bulk and source of MOS. In short, supply voltage variation disturbs Vbs, and Vbs then disturbs Vthp.

$$Vthp = Vthp0 + \gamma_p(\sqrt{2|Vfn| + Vbs} - \sqrt{2|Vfn|}) \quad (1)$$

Referring to threshold voltage's characteristic, the Vthp voltage has a negative temperature coefficient around -1mV/°C, which indicates that it is also affected by temperature.

Thus, the 2 cascaded source followers generate  $2 \times V$ thp voltage, VTout, with VDD and temperature variation.

Fig. 6. Schematic of Voltage & Temperature sensor

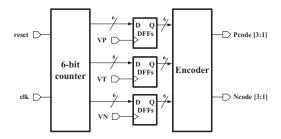

# D. PVT decider

Depending on the above sensors output voltages, PVT decider has to derive two digital codes, Pcode [3:1] and Ncode [3:1], to compensate the  $2\times VDD$  output buffer. PVT decider consists of a  $V_{\rm Bias}$  generator, three comparators, and a Digital circuit, as shown in Fig. 3. Fig. 7 illustrates the block diagram of Digital circuits, where a 6-bit counter, an Encoder, and D flip-flops are included. When pout, TVout, and nout reach the reference voltage VREFP and VREFN, respectively, comparators deliver, VP, VT, and VN, respectively, to latch D flip-flops (DFFs). According to various corners, the Encoder will create two codes, Pcode [3:1] and Ncode [3:1]. The codes indicates the required compensation status to control the output currents in  $2\times VDD$  output buffer.

Fig. 7. Architecture of Digital circuit

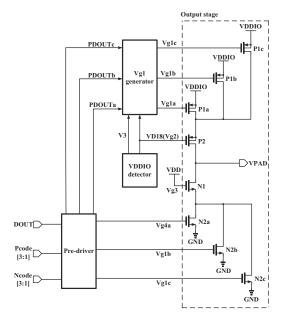

# E. 2×VDD Output Buffer

The 2×VDD output buffer is composed of a Pre-driver, a Vg1 generator, a VDDIO detector, and an output stage, as shown in Fig. 8. Pre-driver is used to encode three control signals, DOUT, Pcode [3:1], and Ncode [3:1], to adjust output currents for slew rate compensation. VDDIO detector and Vg1 generator can generate appropriate gate drive voltages in different voltage modes without leakage currents and overstress problems [7].

Fig. 8. Schematic of 2×VDD mixed-voltage tolerant output buffer

# F. Output stage

Since the supply voltage (VDD) of the core circuits is 1.2 V in 90 nm CMOS process, the output stage must be realized using two groups of stacked PMOS and NMOS transistors, respectively, for transmitting  $2 \times \text{VDD}$  ( $\approx 2.5 \text{ V}$ ) signals, as depicted in Fig. 8. PMOSs P1a $\sim$  P1c are in parallel such that the slew rate of the output signal can be selected by turning on or off the currents flowing through P1a $\sim$ P1c individually. According to the detected different process and temperature status, Pcode [3:1] and Ncode [3:1] will select the number

of turned on PMOSs of output stage. The switching status of N1a~N1c are corresponding to PMOSs mentioned above. P1a~P1c and N1a~N1c are designed with different sizes to generate different currents, which could successfully achieve the required coarse and fine adjustment.

#### III. IMPLEMENTATION AND VERIFICATION

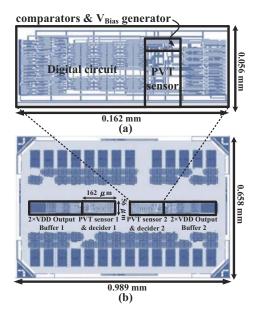

The proposed design is implemented using TSMC 90 nm CMOS technology without any thick-oxide devices. Fig. 9 shows the layout of the proposed design, where the overall chip size is only  $0.658 \times 0.989 \text{ mm}^2$  and the compensation circuit is only  $0.056 \times 0.407 \text{ mm}^2$ . That is, the area overhead is less than 3.6%. Fig. 10 shows the simulation of PVT sensors at different corners. The time of pout hits VREFP given different corners. So are that of VTout and nout. Therefore, the count latched by DFFs will be different such that the Encoder will generates different Pcode [3:1] and Ncode [3:1] accordingly. Therefore, it is easy to distinguish the PVT corners using the 6-bit counter to count the timing. Table I shows the compensation results given different VDDIOs. Apparently, the best improvement is located in VDDIO = 0.9V, and the fastest data rate is 345 MHz when VDDIO = 1.2 V. Table II shows the comparison between our design and several prior works. Our design attains the edge of all corners process detection, including TT, FF, SS, FS, and SF, and maximum slew rate improvement.

Fig. 9. Layout of the proposed design

## IV. CONCLUSION

A robust compensation circuit is proposed in this paper, where the compensation circuit is implemented using a typical 90 nm CMOS process to self-adjust the slew rate of  $2 \times VDD$  output buffer. The maximum slew rare improvement can be

TABLE I COMPENSATION RESULTS AT DIFFERENT VDDIOS

| VDDIO                                                   | 2.5 V                          | 1.8 V                           | 1.2 V           | 0.9 V                            |

|---------------------------------------------------------|--------------------------------|---------------------------------|-----------------|----------------------------------|

| Data rate without compensation (MHz)                    | 250                            | 166                             | 330             | 250                              |

| Data rate with compensation (MHz)                       | 277                            | 172                             | 345             | 285                              |

| △Rise slew rate improvement in different corners (V/ns) | $25\% (0.85 \rightarrow 0.64)$ | $17\% (2.41 \rightarrow 2.01)$  | 25% (1.78→1.33) | $38\% \ (0.45 \rightarrow 0.28)$ |

| △Fall slew rate improvement in different corners (V/ns) | 27% (1.75→1.28)                | $22\% \ (1.5 \rightarrow 1.17)$ | 31% (1.08→0.75) | 30% (0.56→0.39)                  |

Fig. 10. Simulation of the PVT sensor at different corners

achieved over 38%. After compensation, the data rate is also elevated to 345 MHz from 330 MHz when VDDIO = 1.2 V.

### ACKNOWLEDGMENT

This investigation was partially supported by Metal Industries Research Development Centre (MIRDC) and Ministry

TABLE II

PERFORMANCE COMPARISON OF OUTPUT BUFFER

|                             | Ours                 | [2]<br>ISSCC | [3]<br>JSSC | [4]<br>JSSC |

|-----------------------------|----------------------|--------------|-------------|-------------|

| Year                        | 2011                 | 2007         | 2003        | 2003        |

| Process $(\mu m)$           | 0.09                 | 0.18         | 0.35        | 0.18        |

| Results                     | Post-sim             | Post-sim     | Measured    | Measured    |

| Slew rate (V/ns)            | 1.1-2.5              | 2.10-3.58    | 1.60-2.20   | 0.40-0.99   |

| Process corners<br>detected | TT, FF, SS<br>FS, SF | TT, FF, SS   | TT, FF, SS  | TT, FF, SS  |

| Power (mW)                  | 5.6                  | 13.7         | N/A         | N/A         |

| Slew rate improvement       | 38%                  | N/A          | N/A         | 32%         |

of Economic Affairs, Taiwan, under grant 100-EC-17-A-01-1010, 99-EC-17-A-01-S1-104, and 99-EC-17-A-19-S1-133. It was also partially supported by National Science Council, Taiwan, under grant NSC99-2221-E-110-082-MY3, NSC99-2923-E-110-002-MY2, NSC-99-2221-E-110-081-MY3, NSC-99-2220-E-110-001. This research was partially supported by the Southern Taiwan Science Park Administration (STSPA), Taiwan, R.O.C. under contract no. EZ-10-09-44-98. The authors would like to express their deepest gratefulness to CIC (Chip Implementation Center) of NARL (Nation Applied Research Laboratories), Taiwan, for their thoughtful chip fabrication service.

## REFERENCES

- B. Razavi, "Short-channel effects and device models," *Design of Analog CMOS Integrated Circuits, Mcgraw-Hill*, pp. 599-600, 2001.

Y.-H. Kwak, I. Jung, H.-D. Lee, Y.-J. Choi, Y. Kumar, and C. Kim, "A

- [2] Y.-H. Kwak, I. Jung, H.-D. Lee, Y.-J. Choi, Y. Kumar, and C. Kim, "A one cycle lock time slew-rate-controlled output driver," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 408-611, Feb. 2007.

- [3] T. Matano, Y. Takai, T. Takahashi, Y. Sakito, I. Fujii, Takaishi, et al., "A 1-Gb/s/pin 512-Mb DDRII SDRAM using a digital DLL and a slew-rate-controlled output buffer," *IEEE J. Solid-State Circuits*, vol. 38, no. 5, pp. 762-768, May 2003.

- [4] S.-K. Shin, W. Yu, Y.-H. Jun, J.-W. Kim, B.-S. Kong, et al., "A slew rate controlled output driver using PLL as compensation circuit," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1227-1233, Jul. 2003.

- J. Solid-State Circuits, vol. 38, no. 7, pp. 1227-1233, Jul. 2003.

[5] M.-D. Ker, T.-M. Wang, and F.-L. Hu, "Design on mixed-voltage I/O buffers with slew-rate control in low-voltage CMOS process," in Proc. IEEE Int. Conf. on Electronics, Circuits and Syst., pp. 1047-1050, Sep. 2008

- [6] V. Narang, B. Arya, and K. Rajagopal, "Novel low delay slew rate control I/Os," in *Proc. 1st Asia Symp. on Quality Electronic Design*, pp. 189-193, 2009.

- [7] J.-Y. Park, Y. Koo, D.-K. Jeong, W. Kim, C. Yoo, and C. Kim, "A high-speed memory interface circuit tolerant to PVT variations and channel noise," in *Proc. European Solid-State Circuits Conf.*, pp. 293-296, 2001.

- [8] C.-C. Wang, R.-C. Kuo, and J.-W. Liu, "0.9 V to 5 V bidirectional mixed-voltage I/O buffer with an ESD protection output stage," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 8, pp. 612-616, Aug. 2010