# A 12-bit Current-Steering DAC with Output Impedance Compensation for PNN Prototyping

Pradyumna Vellanki\*, Jun-Yu Chang\*, Friedel Gerfers<sup>†</sup>, Yung-Jr Hung<sup>‡</sup>, Chewn-Pu Jou<sup>§</sup>, and Chua-Chin Wang\*

\*Department of Electrical Engineering, National Sun Yat-sen University, Kaohsiung, Taiwan 80424

<sup>†</sup>Technische Universität Berlin, Berlin, Germany 10623

<sup>‡</sup>Department of Photonics, National Sun Yat-sen University, Kaohsiung, Taiwan 80424 <sup>§</sup>Taiwan Semiconductor Manufacturing Company, Hsinchu Science Park, Hsinchu, Taiwan 30075 Email: ccwang@ee.nsysu.edu.tw

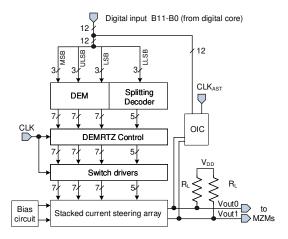

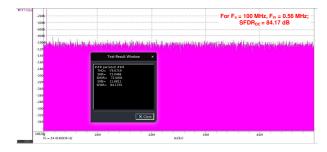

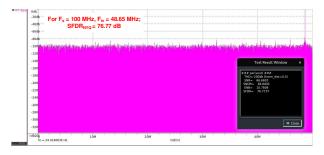

Abstract—This article presents the design and implementation of a highly linear and output impedance compensated digitalto-analog converter (DAC). The proposed architecture minimizes layout area while maintaining high linearity and optimized output impedance. The DAC comprises several key functional blocks, including a Stacked current steering array, a Dynamic Element Matching Coder (DEM), a Splitting Decoder, a Dynamic Element Matching and Full Differential Current Return-to-Zero Logic Controller (DEMRTZ Control), a Switch Driver Array, a Bias Circuit, and an Output Impedance Compensation (OIC) module. Each component plays a crucial role in improving the overall performance of the DAC in terms of linearity and impedance characteristics. The proposed DAC is designed using TSMC TN40G process technology with a core circuit area of 242.555  $\times$  166.2  $\mu m^2$ . Post-layout simulations show that at an input frequency of 0.56 MHz, the DAC achieves an ENOB of 11.68 bits and an SFDR of 84.17 dB. At 48.65 MHz, the DAC maintains an ENOB of 10.78 bits and an SFDR of 76.77 dB.

Index Terms-PNN, MZM, DAC, DEMRTZ, SFDR, OIC

## I. INTRODUCTION

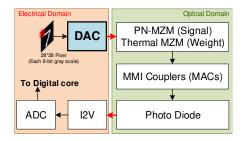

Photonic neural networks (PNNs) have emerged as a promising solution for next-generation AI systems [1]. However, the realization of PNNs requires sophisticated analog-todigital (ADC) and digital-to-analog conversion (DAC) technologies that can interface effectively with both the digital and photonic components of the system. A key component of PNN is the Mach-Zehnder Modulator (MZM), which converts electrical signals into optical signals and enables critical operations like matrix-vector multiplications. The performance of MZMs heavily relies on their driving electronics, particularly digital-to-analog converters (DACs) [2]. The Current-Steering DAC (CS-DAC) architecture is well-suited for this task due to its speed and scalability [3]-[6]. However, challenges arise in adapting it to meet the interface demands of MZMs used in PNNs. The basic requirements of MZMs are tabulated in Table. I. A PNN prototype realized by our team is demonstrated in Fig. 1. This research is focused on designing a wide-range CS-DAC with reasonable speed trade-offs and high current cell impedance to minimize the effect of the finite impedance of conventional CS-DACs. This work presents an advanced CS-DAC architecture that incorporates output impedance compen-

Partial financial support for this work has been provided by the NSTC, Taiwan, specifically through the grants NSTC 113-2923-E-110-001-, and NSTC 112-2218-E-110-009-.

TABLE I MZM BASIC REQUIREMENTS

| Parameters           | Value        |

|----------------------|--------------|

| V <sub>in</sub> (V)  | 0.03 to 3    |

| Speed (Hz)           | 100 M to 1 G |

| Impedance $(\Omega)$ | 50           |

Fig. 1. The prototype of the PNN system

Fig. 2. Block diagram of 12-bit CS-DAC with output impedance compensation

sation and dynamic element matching techniques to enhance performance and minimize layout area.

## II. PROPOSED 12-BIT CS-DAC WITH OUTPUT IMPEDANCE COMPENSATION

The proposed DAC architecture consists of multiple functional blocks that collectively improve linearity and output

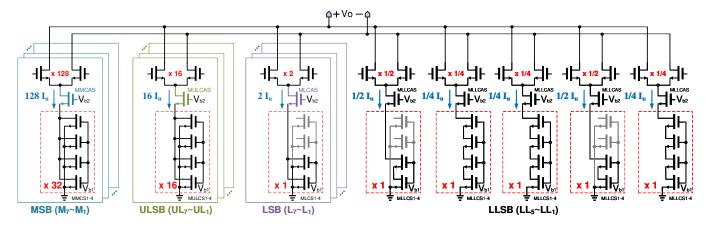

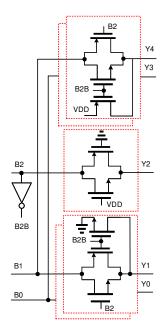

Fig. 3. Schematic of Stacked current steering array

impedance stability as shown in Fig. 2: a Stacked current steering array, Bias Circuit, a Dynamic Element Matching Coder (DEM), a Dynamic Element Matching and Full Differential Current Return-to-Zero Logic Controller (DEMRTZ Control), Switch drivers array, and an Output Impedance Compensation (OIC) circuit.

The digital input B11-B0 is segmented into three unary MSB bits, three unary ULSB bits, three unary LSB bits, and three binary LLSB bits. The operating principle involves processing the upper 9 bits and the lower 3 bits separately through the DEM Coder and the Splitting Decoder, respectively. The DEM Coder encodes the input signal to generate a control signal, while the Splitting Decoder decodes the input signal to produce a split code, which is then sent to the DEMRTZ Control circuit. The DEM Coder is sourced from our previous work [7]. Based on the DEMRTZ output, the Switch driver circuit manipulates the switch pairs of the current source to generate a return-to-zero (RTZ) differential DAC output, given by VDAC = Vout1 - Vout0 = 0. Additionally, an OIC circuit is incorporated between Vout1 and Vout0 to compensate for the Spurious-Free Dynamic Range (SFDR) attenuation caused by limited output impedance.

# A. Current sources schematic of the Stacked current steering array

Fig. 3 illustrates the Current sources schematic of the Stacked current steering array, where Cascode transistors MMCAS, MULCAS, MLCAS, and MLLCAS mitigate output impedance limitations by operating in the saturation region. Each current source MMCS1 – MMCS4, MULCS1 – MULCS4, MLCS1 – MLCS4, and MLLCS1 – MLLCS4 is divided into four transistors to minimize mismatches from etching variations and enhance performance.

Differences in transistor count within current source switch pairs lead to parasitic capacitance variations. A Compensation capacitor is introduced between the switch driver circuit and the current source switch pair to reduce timing skew, ensuring uniform signal timing and improved DAC performance. Fig. 4 shows the compensation capacitor positioning.

Fig. 4. Compensation capacitor

#### B. Splitting Decoder

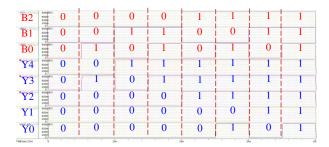

Fig. 5 illustrates the Splitting Decoder, which converts a three-bit input into five outputs, as detailed in Table II. Its simplified Boolean algebra representation is provided in Eqn. (1). The logic is implemented using transmission gates, NMOS, and PMOS transistors, resulting in a more area-efficient design compared to traditional logic gate-based implementations.

$$Y4 = B2 + B1; Y3 = B2 + B0; Y2 = B2;$$

$Y1 = B2 \cdot B1; Y0 = B2 \cdot B0$  (1)

To mitigate nonlinearities caused by binary current source switching during intermediate code transitions, the lowest three bits (LLSB), B2–B0, are encoded into a five-bit split code, Y4–Y0. The current weights are redistributed from 4Iu, 2Iu, Iu to 2Iu, Iu, Iu, 2Iu, Iu, effectively reducing current variations during switching. This approach minimizes abrupt changes in the current, thereby improving linearity. For instance, during the transition of B2–B0 from 011 to 100, only Y2 switches from 0 to 1, requiring the activation of just one Iu switch. Compared to conventional binary-weighted current source switching, this method significantly reduces transient current variations and mitigates differential nonlinearity (DNL) errors.

#### TABLE II SPLITTING DECODER TRUTH TABLE

| Bit | nary in | put | Splitting Decoder output |    |    |    |    |  |

|-----|---------|-----|--------------------------|----|----|----|----|--|

| B2  | B1      | B0  | Y4                       | Y3 | Y2 | Y1 | Y0 |  |

| 0   | 0       | 0   | 0                        | 0  | 0  | 0  | 0  |  |

| 0   | 0       | 1   | 0                        | 1  | 0  | 0  | 0  |  |

| 0   | 1       | 0   | 1                        | 0  | 0  | 0  | 0  |  |

| 0   | 1       | 1   | 1                        | 1  | 0  | 0  | 0  |  |

| 1   | 0       | 0   | 1                        | 1  | 1  | 0  | 0  |  |

| 1   | 0       | 1   | 1                        | 1  | 1  | 0  | 1  |  |

| 1   | 1       | 0   | 1                        | 1  | 1  | 1  | 0  |  |

| 1   | 1       | 1   | 1                        | 1  | 1  | 1  | 1  |  |

Fig. 5. Splitting Decoder

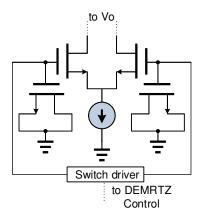

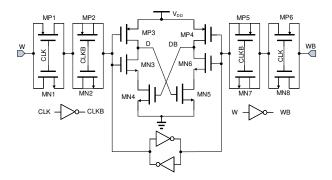

#### C. Switch driver circuit

To synchronize the input signal in high-speed circuits, a Switch Driver is used to compensate for delays between the DEM and DEMRTZ Control, as shown in Fig. 6. When the signal crossover point is at  $(V_{\rm DD}/2),$  insufficient bias voltage can simultaneously turn off the current sources, causing surges. The circuit raises the crossover point to prevent this issue. Additionally, to minimize surges from channel charge injection and clock feedthrough, a dummy switch is incorporated to stabilize the control signal during transitions.

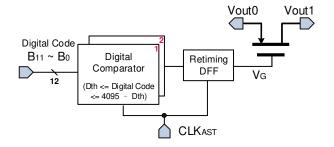

## D. Output impedance compensation (OIC)

Fig. 7 illustrates the OIC implementation, which comprises a Digital Comparator, Retiming DFF, and PMOS. In a two-stage VG generator, the compensation strategy is most effective when the digital input code is at the lower and upper extremes, as these regions exhibit greater imbalance in the scale [8]. Simulations were conducted with 128, 256, 512, and 1024 digital input values to determine the optimal compensation point. The results indicated that setting the compensation at 256 and 512 yielded the best performance, with both values producing nearly identical outcomes. Ultimately,

Fig. 6. Schematic of the Switch driver

Fig. 7. Output Impedance Compensation

Fig. 8. Floor plan and layout

256 was selected as the final setting. Consequently, when the Digital Code is below 256 or above 3839 (where 3839 originates from 4095 - 256 in a 12-bit system spanning 0 to 4095), the PMOS operates in the cut-off region with high resistance to reduce approximation errors. Between 256 and 3839, it functions in the linear region to approximate the ideal resistance. Additionally, the assistant clock (CLK\_{AST}) ensures proper  $V_{\rm G}$  switching timing during the RTZ phase, minimizing nonlinear effects and improving SFDR by 7 dB.

#### III. POST LAYOUT SIMULATIONS

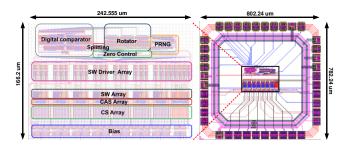

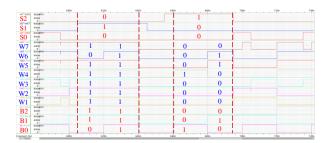

The proposed work is designed using TSMC TN40G process with a core circuit area of 242.555  $\times$  166.2  $\mu m^2$  and a full-chip layout area of 802.24  $\times$  782.24  $\mu m^2$ , as shown in Fig. 8. It operates at 100 MHz with a power dissipation of 9.51 mW. Fig. 9 shows the simulated waveform diagram of the DEM Coder circuit. Fig. 10 shows the post-layout simulation, which verifies the Splitting Decoder circuit functioning and its truth table. When the digital input codes B2 $\sim$ B0 switch from

Fig. 9. DEM output waveforms

Fig. 10. Splitting encoder waveform

Fig. 11. TT, 25, 0.9 V, 0.56 MHz

Fig. 12. TT, 25, 0.9 V, 48.65 MHz

011 to 100, the output will only turn on the Y2 current source, effectively reducing the generation of glitches and suppressing DNL. In the post-layout simulations, the worst DNL and INL at the 4096 sampling points are 0.7628 LSB and 0.5175 LSB, respectively. At 0.56 MHz, the DAC achieves an ENOB of 11.68 bits and SFDR of 84.17 dB, as shown in Fig. 11 and Fig. 12 illustrates the SFDR performance at a higher input frequency of 48.65 MHz, where the DAC achieves an ENOB of 10.78 bits and an SFDR of 76.77 dB. Our work is compared with previous designs, as summarized in Table III.

TABLE III

PERFORMANCE COMPARISON

| Parameter                | [3]     | [4]     | [5]     | [6]     | Our work |

|--------------------------|---------|---------|---------|---------|----------|

| Technology               | 130 nm  | 180 nm  | 180 nm  | 28 nm   | 40 nm    |

| Resolution               | 12 bits | 10 bits | 12 bits | 12 bits | 12 bits  |

| f <sub>s</sub> (MS/s)    | 100     | 500     | 500     | 1000    | 100      |

| Supply<br>Voltage (V)    | 1.5/1.2 | 1.8     | 1.8/1.2 | 1.5/0.9 | 0.9      |

| Area (mm <sup>2</sup> )  | 0.21    | 0.33    | 0.18    | 0.26    | 0.0403   |

| SFDR <sub>DC</sub> (dB)  | 68.3    | 72.8    | 68.8    | 81      | 84.18    |

| SFDR <sub>NYQ</sub> (dB) | 62      | 70.12   | 62.1    | 65      | 76.77    |

| I <sub>load</sub> (mA)   | 16      | 10      | 6       | 8       | 8        |

| P <sub>total</sub> (mW)  | 18      | 30.24   | 17.2    | 33      | 9.51     |

| FOM                      | 0.49    | 3.9     | 2.8     | 5.5     | 140      |

$FOM = \frac{2 \frac{(SFBR_{NYQ} - 1.16)}{6.02} \cdot f_s}{A_{POS}} \times 10^{-6}$

#### IV. CONCLUSION

This paper presents a highly linear and output impedance compensated current steering DAC with an efficient layout and enhanced dynamic performance. The integration of DEM, DEMRTZ control, and OIC significantly improves linearity and impedance characteristics, making it a suitable solution for high-speed and high-resolution applications like PNN systems. Post-layout simulations confirm the effectiveness of the design, demonstrating an ENOB of 11.68 bits and an SFDR of 84.17 dB at 0.56 MHz, and an ENOB of 10.78 bits and an SFDR of 76.77 dB at 48.65 MHz. These results validate the proposed techniques in achieving high performance. High SFDR is crucial for minimizing distortion in optical modulation, making the DAC well-suited for driving MZM. Future work will focus on further optimizing power efficiency and exploring advanced compensation techniques for improved performance.

### REFERENCES

- [1] B. J. Shastri *et al.*, "Photonics for artificial intelligence and neuromorphic computing," *Nature Photonics*, vol. 15, no. 2, pp. 102–114, 2021

- [2] C. Huang et al., "Prospects and applications of photonic neural networks," Advances in Physics: X, vol. 7, no. 1, 2022.

- [3] W. Mao et al., "High dynamic performance current-steering DAC design with nested-segment structure," *IEEE Trans. on Very Large Scale Integration (VLSI) Syst.*, vol. 26, no. 5, pp. 995-999, May 2018.

- [4] S. Samanta et al., "A pairwise swap enabled randomized DEM addressing intersegment mismatch for current steering digital-to-analog converters," *IEEE Trans. on Very Large Scale Integration (VLSI) Syst.*, vol. 30, no. 9, pp. 1332-1340, Sept. 2022.

- [5] X. Tong et al., "A 12-bit current-steering DAC with unary- splitting binary segmented architecture and improved decoding circuit topology," *IEEE Trans. on Very Large Scale Integration (VLSI) Syst.*, vol. 30, no. 10, pp. 1391-1400, Oct. 2022.

- [6] C.-U. Park et al., "A 12-bit 1GS/s current-steering DAC with paired current source switching background mismatch calibration," in Proc. 2023 IEEE Custom Integr. Circuits Conf. (CICC), pp. 1-2, Apr. 2023.

- [7] C.-C. Wang et al., "A 12-bit 100-Msps DAC with 75.3 dB SFDR using randomized biasing current source selection for real-time FOG systems," in Proc. 2021 9th Int. Symp. on Next Gener. Electronics (ISNE), pp. 1-4, July 2021.

- [8] H.-Y. Huang et al., "A 0.07-mm2 162-mW DAC achieving >65 dBc SFDR and < -70 dBc IM3 at 10 GS/s with output impedance compensation and concentric parallelogram routing," IEEE J. of Solid-State Circuits, vol. 55, no. 9, pp. 2478-2488, Sept. 2020.</p>